# SRI CHANDRASEKHARENDRA SARASWATHI VISWA MAHAVIDYALAYA

(University established under section 3of UGC Act 1956) (Accredited with 'A' Grade by NAAC) Enathur, Kanchipuram – 631 561

### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

Lab Manual VLSI Design Lab B.E(FULL TIME) III YEAR, VI<sup>th</sup> SEMESTER

Prepared by:

G.Poornima, Assistant Professor

## Index

| EX.NO | NAMEOF THE EXPERIMENTS                                | PAGE<br>NO | SIGN |

|-------|-------------------------------------------------------|------------|------|

|       | CYCLE- I                                              |            |      |

|       | Tools- XILINX ISE 14.1                                |            |      |

| 1     | Design Entry and Simulation of Combinational Circuits |            |      |

| 2     | Place and Route and Post Place & Route Simulation     |            |      |

| 3     | Design and FPGA Implementation of Combinational       |            |      |

| 4     | Design and FPGA Implementation of Sequential Circuits |            |      |

| 5     | Analysis of Area, Power and Delay For Sequential      |            |      |

| 6     | Invoke PLL to generate Real Time Clock                |            |      |

|       | CYCLE-II                                              |            |      |

|       | Tools – LT-SPICE and ELECTRIC VLSI System             |            |      |

|       | Design EDA                                            |            |      |

| 7     | Ring Oscillator                                       |            |      |

| 8     | Differential Amplifier                                |            |      |

| 9     | CMOS Inverter                                         |            |      |

| 10    | Layout CMOS Inverter                                  |            |      |

| 11    | CMOS Inverter – Place and Route                       |            |      |

| 12    | Layout CMOS NAND Gate                                 |            |      |

|       | Study Experiments<br>Tools- Synopsys                  |            |      |

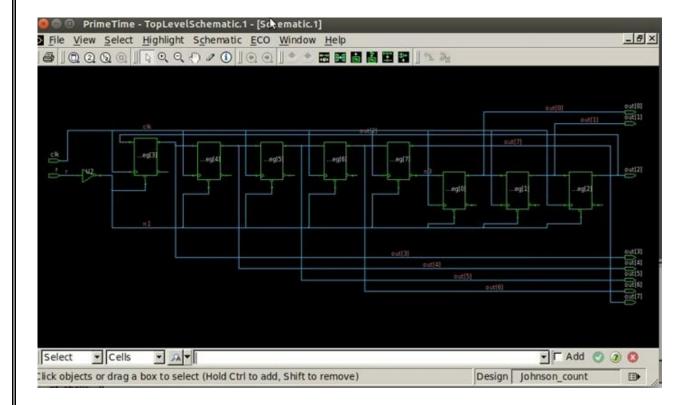

| 13    | Static Timing Analysis                                |            |      |

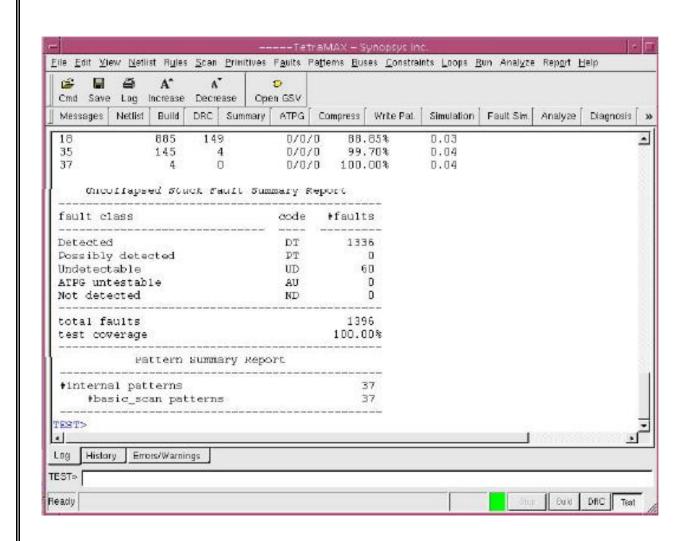

| 14    | DfT-Scan Chain Insertion                              |            |      |

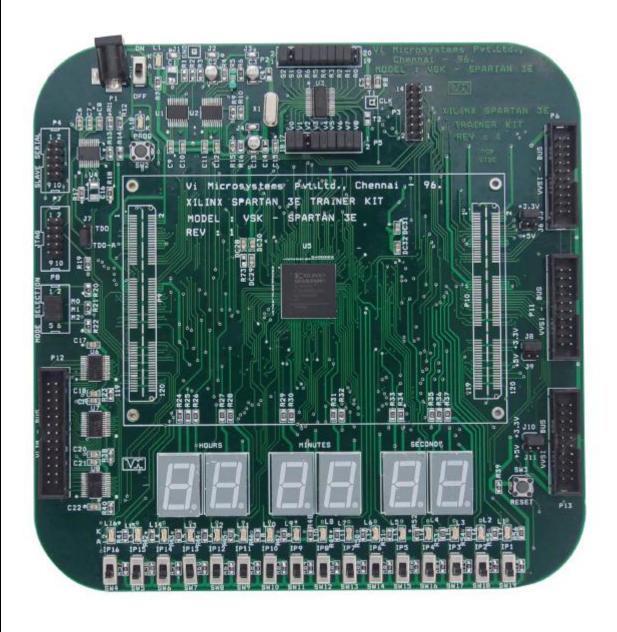

### XILINX SPARTAN 3E TRAINER KIT

The Spartan-3E Trainer Kit is a demonstration platform intended to become familiar with the new features and availability of the Spartan-3E FPGA family. This Kit provides a easy-to-use development and evaluation platform for Spartan-3E FPGA designs.

### Slide Switch connections with FPGA - INPUT PIN

| FPGA PINS |

|-----------|

| T14       |

| T12       |

| Т9        |

| T7        |

| T2        |

| G12       |

| H1        |

| R3        |

| N11       |

| N3        |

| M13       |

| M7        |

| M3        |

| K4        |

| J12       |

| J11       |

|           |

### **OUTPUT PINS**

| FPGA PINS |

|-----------|

| R1        |

| R2        |

| K3        |

| T4        |

| T5        |

| R6        |

| T8        |

| R10       |

| N10       |

| P12       |

| N9        |

| N12       |

| P13       |

| R13       |

| T13       |

| P14       |

|           |

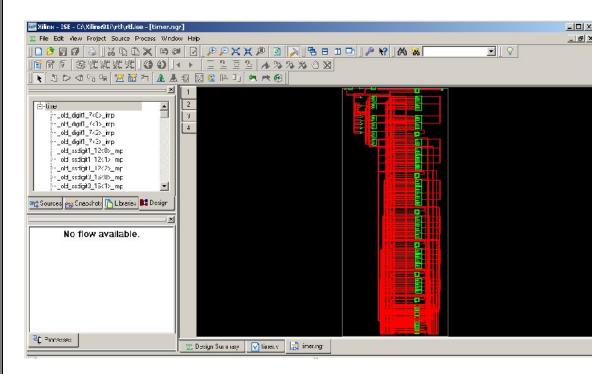

### $\label{procedure} Procedure \ for \ simulation and implementation of Xilinx tool and FPGA$

### STEP1:

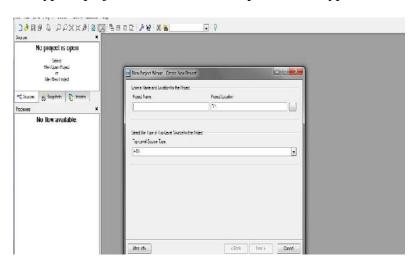

ClickXilinxISE9.1

### STEP2:

File->NewprojectandtypetheprojectnameandcheckthetoplevelsourcetypeasHDL

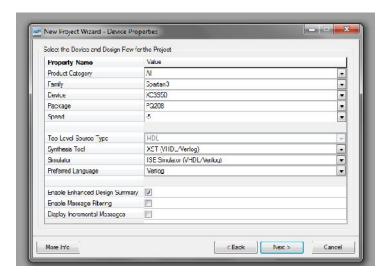

STEP3:Checkthedevicepropertiesandclicknext

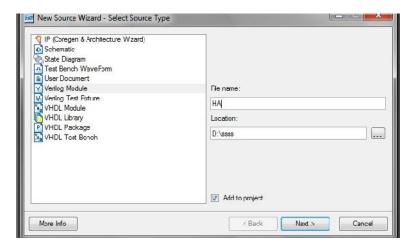

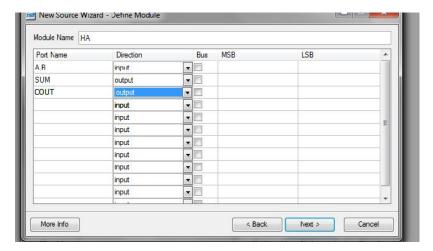

### STEP4: Click New Source And Select the Verilog Module and then give the file name and the source And Select the Verilog Module and then give the file name and the source And Select the Verilog Module and then give the file name and the source And Select the Verilog Module and the new Module and the source And Select the Verilog Module and the new Module and the source And Select the Verilog Module and the new Module and the n

### STEP5:

Select theInput,Outputportnamesandclickfinish.

### STEP6:

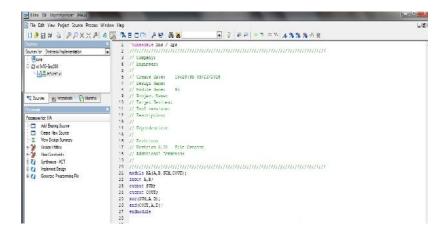

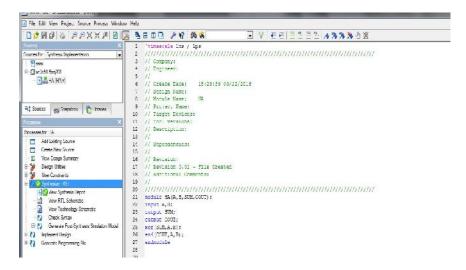

Typetheprogramandsaveit

### STEP7:CheckthesynthesizeXSTandchecksyntax

STEP8: Select user constraints-> assign package pins, set port numbers and save it then selectIOBusdelimiterasXSTdefault<>->clickok

### STEP9:

Doubleclickimplementdesign and clickgenerateprogrammingfile->configuredevice (impact)->finishthenselectbitfile

### STEP10:

Rightclickonthexc3s400figure->program-

$>\!\!filename then click finish and Finally check the functionality in hardware$

| EXP NO: 1 |                                                              |

|-----------|--------------------------------------------------------------|

| EAI NO. I | <b>Design Entry and Simulation of Combinational Circuits</b> |

| D 4       | Design Entry and Simulation of Combinational Circuits        |

| Date:     |                                                              |

| Date.     |                                                              |

#### AIM:

To writeaVerilogcodeforthe 4bit Ripple carry adderand 4 bit Comparatorand simulateit usingXilinxproject navigator.

### **APPARATUS REQUIRED:**

| S.No | Nameofthe equipment/ software | Quantity |

|------|-------------------------------|----------|

| 1.   | PC with Windows               | 1        |

| 2.   | XilinxProject navigator       | 1        |

### **PROCEDURE:**

- Start theXilinxISE byusing Start → Programfiles → XilinxISE → project navigator

- 2. Click File→New Project

- 3. Enter the Project Name and select the location then click next

- 4. Select the Device and other category and click next twice and finish.

- 5. Click on the symbol of FPGA device and then right click → click on new source.

- 6. Select the Verilog Module and give the filename → click next and define ports → click next and finish.

- 7. Writingthe VerilogCodein VerilogEditor.

- 8. Run the Check syntax→Process window→synthesize→ double click check syntax.If anyerrorsfound then remove theerrors with proper syntax&coding.

- 9. Click on the symbol of FPGA device and then right click → click on new source.

- 10. Select the TestBench Waveformand give the filename → selectentity click next and finish.

- 11. Select thedesired parameters for simulating your design. In this case combinational circuitand simulation time click finish.

- 12. Assign all inputsignal using justclick ongraphand save file.

- 13. From the sourceprocesswindow. ClickBehavioral simulation from drop-down menu

- 14. Select thetest benchfile (.tbw) and click processbutton → double clickthe SimulationBehavioral Model

- 15. Verify your design inwavewindow byseeingbehavior of output signal with respect to input signal

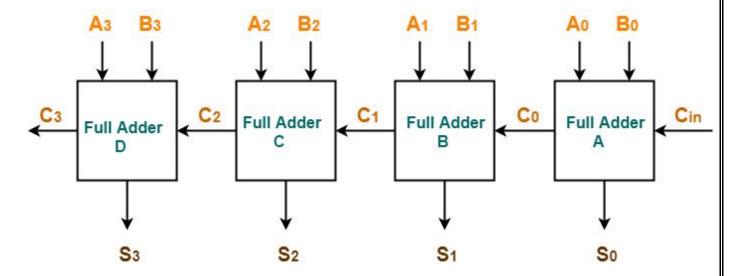

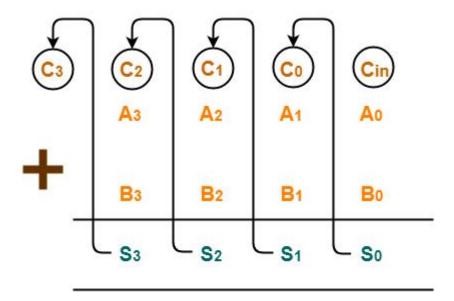

### 4-Bit Ripple Carry Adder

### **Block Diagram:**

4-bit Ripple Carry Adder

Adding two 4-bit Numbers

### **CODING:**

```

module ripple_carry_adder(a, b, cin, sum, cout);

input [03:0] a;

input [03:0] b;

input cin;

output [03:0] sum;

output cout;

wire [2:0]c;

fulladd a1(a[0],b[0],cin, sum[0],c[0]);

fulladd a2(a[1],b[1],c[0],sum[1],c[1]);

fulladd a3(a[2],b[2],c[1],sum[2],c[2]);

fulladd a4(a[3],b[3],c[2],sum[3],cout);

endmodule

module fulladd(a,b,cin,sum,cout);

input a,b,cin;

output sum, cout;

assign sum=(a^b^cin);

assign cout=((a&b)|(b&cin)|(a&cin));

endmodule

```

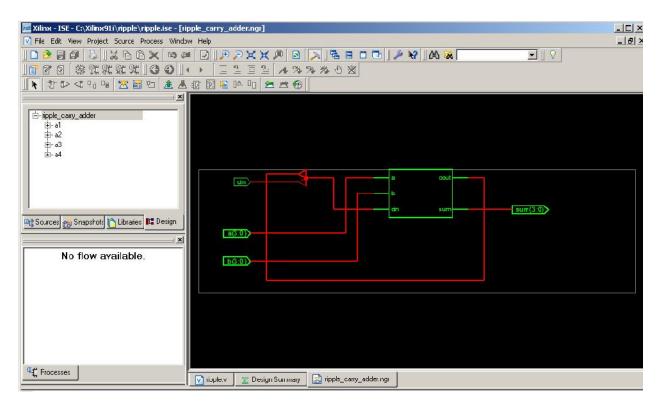

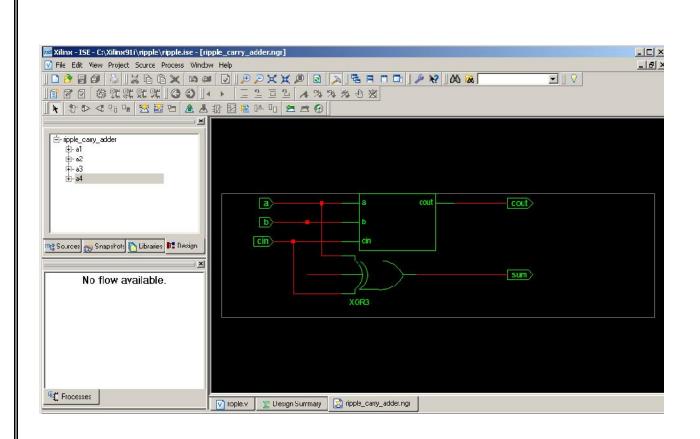

### **RTL SCHEMATIC:**

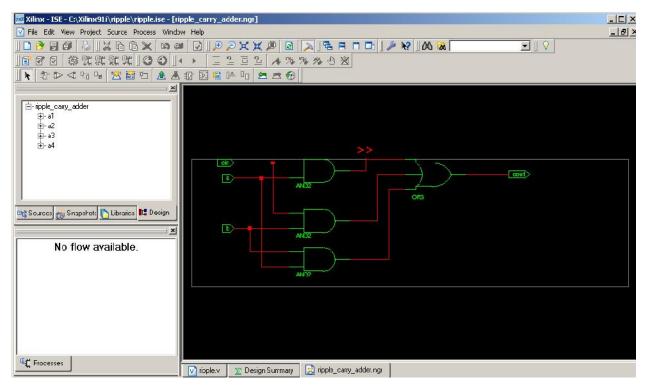

### **TECHNOLOGY SCHEMATIC:**

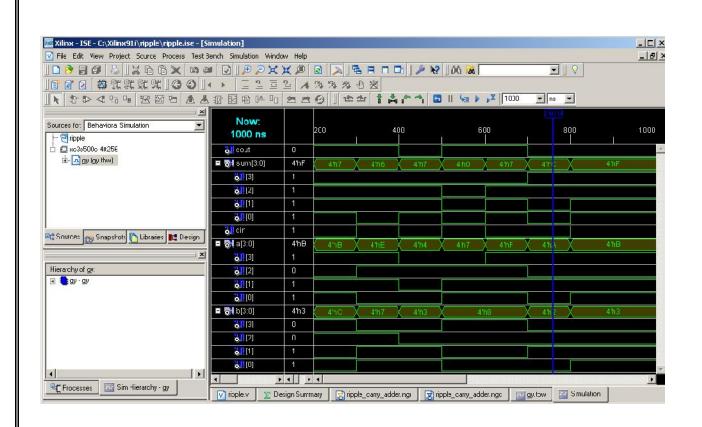

### **SIMULATION OUTPUT:**

### **RESULT:**

Thus the Verilog code for 4 bit Ripple Carry Adder is simulated using Xilinx project navigator.

### AIM:

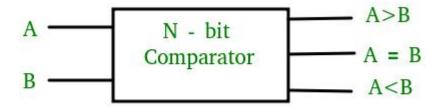

To synthesis 4- Bit Comparator and then Place& Route and Post Place & Root using Implementation option available in Xilinx project navigator.

### **APPARATUS REQUIRED:**

| S.No | S.No Nameofthe equipment/ software |   |

|------|------------------------------------|---|

| 1.   | PC with Windows                    | 1 |

| 2.   | XilinxProject navigator            | 1 |

### Theory:

- > Back annotation is the translation of a routed or fitted design to a timing simulation netlist.

- > To define the behavior of the FPGA, a hardware description language (HDL) or a schematic design methods are used. Common HDLs are VHDL and Verilog. Then, using an electronic design automation (EDA) tool, a technology-mapped net list is generated.

- > The net list can then be fitted to the actual FPGA architecture using a process called place and-route, usually performed by the FPGA vendor place-and-route software.

- ➤ The user will validate the map, place and route results via timing analysis, simulation, and other verification methodologies. Once the design and validation process is complete, the binary file generated is used to (re)configure the FPGA.

- ➤ In an attempt to reduce the complexity of designing in HDLs, which have been compared to the equivalent of assembly

- ➤ In a typical design flow, an FPGA application developer will simulate the design at multiple stages throughout the design process.

- ➤ Initially the RTL description in VHDL or Verilog is simulated by creating test benches to simulate the system and observe results.

- > Then, after the synthesis engine has mapped the design to a net list, the net list is translated to a gate level description where simulation is repeated to confirm the synthesis proceeded without errors.

- Finally the design is laid out in the FPGA at which point propagation delays can be added and the simulation run again with these values back-annotated onto the net list.

- ➤ Place & Route, the process of optimization of logic cells for effective utilization of FPGAarea and the speed of operation, is used to modify and infer the following:

- 1. Re-assignment of Pins

- 2. Re-location of Slices

- 3. Run time minimization

### **Procedure:**

- 1. Start the Xilinx ISE by using Start  $\rightarrow$  Program files  $\rightarrow$  Xilinx ISE  $\rightarrow$  project navigator

- 2. Click File→ New Project

- 3. Enter the Project Name and select the location then click next

- 4. Select the Device and other category and click next twice and finish.

- 5. Click on the symbol of FPGA device and then right click  $\rightarrow$  click on new source.

- 6. Select the Verilog Module and give the file name →click next and define ports →click next and finish.

- 7. Writing the Verilog Code in Verilog Editor.

- 8. Run the Check syntax → Process window→ synthesize→ double click check syntax. If any errors found then remove the errors with proper syntax & coding.

- 9. Synthesis your design, from the source window select, synthesis/implementation from the window Now double click the Synthesis -XST

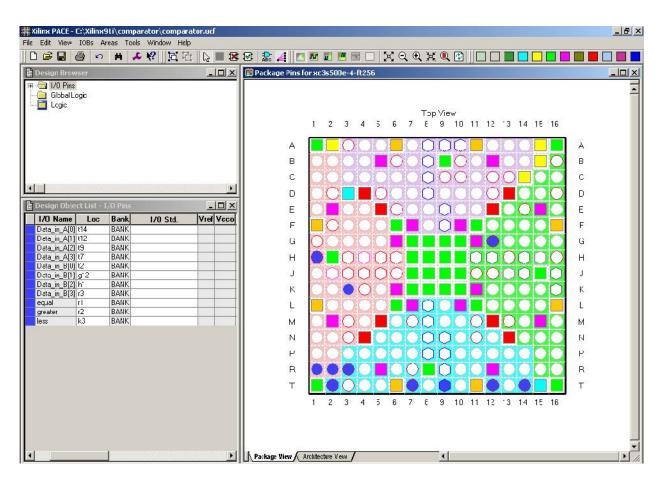

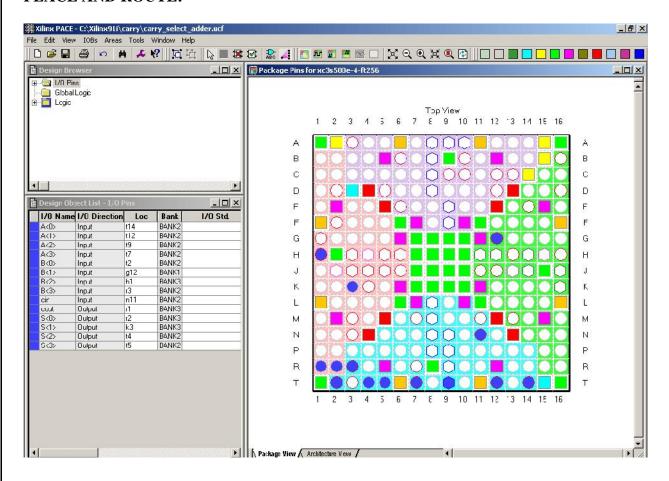

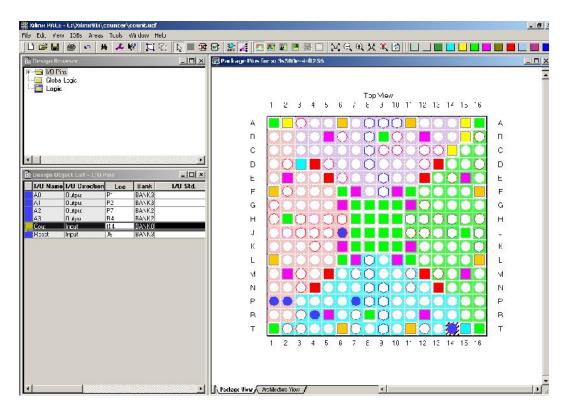

- 10. After Synthesis you assign the Pin Value for your design so, →double click the Assign Package Pins

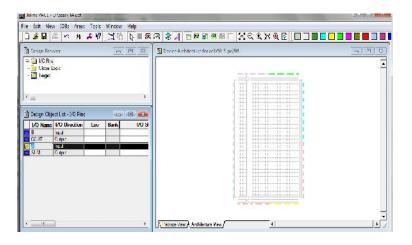

- 11. Enter the Pin value for your input and output signals. if you want see your Pin assignment in FPGA zoom in Architecture View or Package View

- 12. Check the Pins in FPGA. Save file as XST Default click ok and close the window

- 13. Design Implementation begins with the mapping or fitting of a logical design file to a specific device and is complete when the physical design is successfully routed and a bit stream is generated. Double Click Implementation Design.

- 14. After finishing the Implementation, you can view the Implementation report.

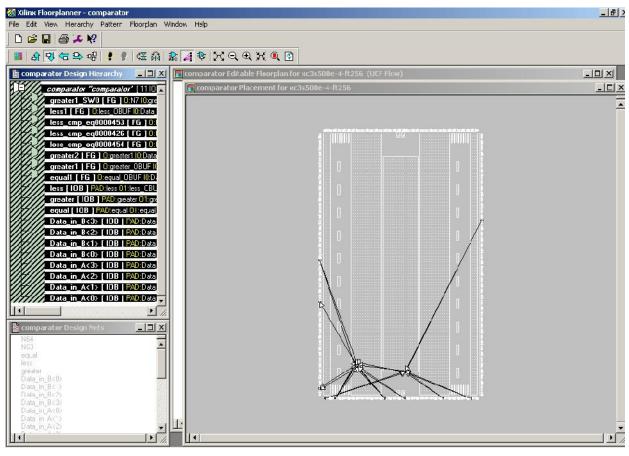

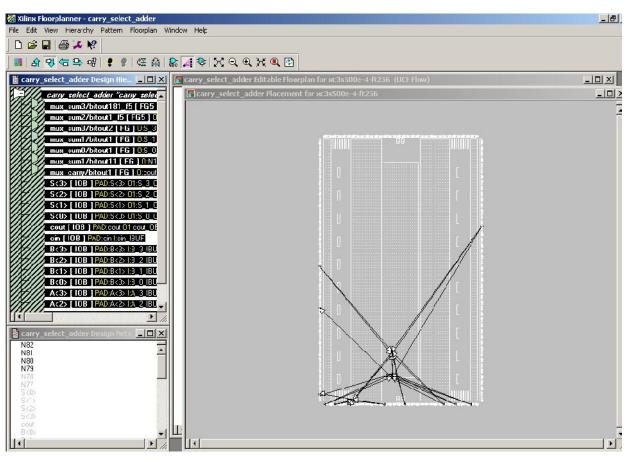

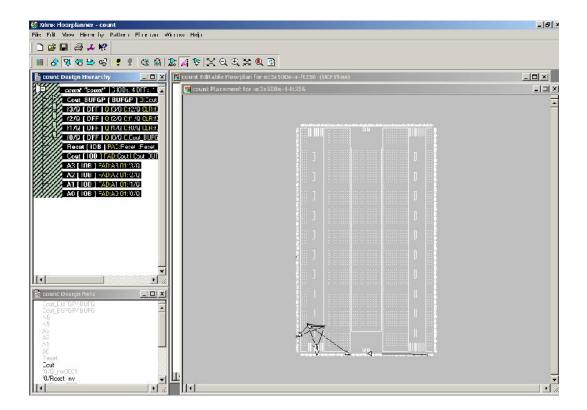

- 15. After implementation you see Design Summary, you get the all details about your design. If you want edit the place and route double click View/Edit placed design

- 16. Check where your IOs are placed in FPGA. And zoom to view how Pins are placed in FPGA. You can see where your pins are placed

- 17. Just double click View/Edit Routed Design to view interconnection wires and blocks

- 18. Click the pin to see where its placed in FPGA. And Zoom particular area to see Place and Routing.

- 19. If required to change the place of the design, click and trace to another slice. View changed place and route of the design

- 20. Double click Back annotated Pin Location. Once back annotation is completed, constraint file is generated.

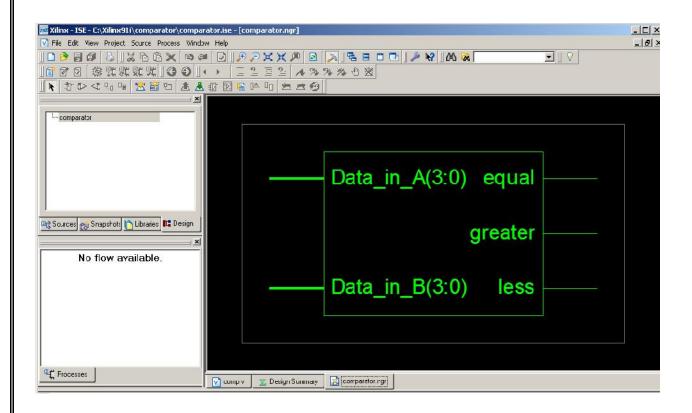

### Block Diagram:

### **Truth Table**

|    | INPUT |    |    | OU                                           | TPUT |     |

|----|-------|----|----|----------------------------------------------|------|-----|

| A1 | A0    | B1 | BO | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B  | A>B |

| 0  | 0     | 0  | 0  | 0                                            | 1    | 0   |

| 0  | 0     | 0  | 1  | 1                                            | 0    | 0   |

| 0  | 0     | 1  | 0  | 1                                            | 0    | 0   |

| 0  | 0     | 1  | 1  | 1                                            | 0    | 0   |

| 0  | 1     | 0  | 0  | 0                                            | 0    | 1   |

| 0  | 1     | 0  | 1  | 0                                            | 1    | 0   |

| 0  | 1     | 1  | 0  | 1                                            | 0    | 0   |

| 0  | 1     | 1  | 1  | 1                                            | 0    | 0   |

| 1  | 0     | 0  | 0  | 0                                            | 0    | 1   |

| 1  | 0     | 0  | 1  | 0                                            | 0    | 1   |

| 1  | 0     | 1  | 0  | 0                                            | 1    | 0   |

| 1  | 0     | 1  | 1  | 1                                            | 0    | 0   |

| 1  | 1     | 0  | 0  | 0                                            | 0    | 1   |

| 1  | 1     | 0  | 1  | 0                                            | 0    | 1   |

| 1  | 1     | 1  | 0  | 0                                            | 0    | 1   |

| 1  | 1     | 1  | 1  | 0                                            | 1    | 0   |

```

//declare the Verilog module - The inputs and output signals.

module comparator(

Data_in_A, //input A

Data_in_B, //input B

//high when A is less than B

less,

equal,

//high when A is equal to B

//high when A is greater than B

greater

);

//what are the input ports.

input [3:0] Data_in_A;

input [3:0] Data_in_B;

//What are the output ports.

output less;

output equal;

output greater;

//Internal variables

reg less;

reg equal;

reg greater;

//When the inputs and A or B are changed execute this block

always @(Data_in_A or Data_in_B)

begin

if(Data_in_A > Data_in_B) begin //check if A is bigger than B.

less = 0;

equal = 0;

greater = 1; end

else if(Data_in_A == Data_in_B) begin //Check if A is equal to B

less = 0;

equal = 1;

greater = 0; end

else begin //Otherwise - check for A less than B.

less = 1:

equal = 0;

greater =0;

end

end

endmodule

```

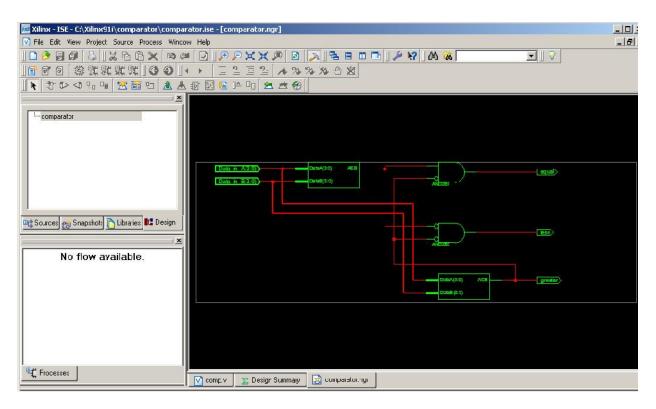

### **TECHNOLOGY SCHEMATIC:**

| RESULT:                                                                                             |

|-----------------------------------------------------------------------------------------------------|

| RESULT.                                                                                             |

| Thus, the Place and Route and Post Place and Route using Implementation options available in Xilinx |

| project navigator were synthesized for 4-bit Comparator.                                            |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

|                                                                                                     |

| EXP NO: 3 | Design and FPGA Implementation of Combinational |

|-----------|-------------------------------------------------|

| Date:     | Circuits                                        |

#### AIM:

To design and implement Booth Multiplier and Carry select Adder in FPGA Spartan 3E Trainer kit using Xilinx project navigator.

### **APPARATUS REQUIRED:**

| S.No | S.No Nameofthe equipment/ software |   |

|------|------------------------------------|---|

| 1.   | PC with Windows                    | 1 |

| 2.   | XilinxProject navigator            | 1 |

#### **PROCEDURE:**

- 1. Start the Xilinx ISE by using Start → Program files → Xilinx ISE → project navigator

- 2. Click File→ New Project

- 3. Enter the Project Name and select the location then click next

- 4. Select the Device and other category and click next twice and finish.

- 5. Click on the symbol of FPGA device and then right click → click on new source.

- 6. Select the Verilog Module and give the file name →click next and define ports →click next and finish.

- 7. Writing the Verilog Code in Verilog Editor.

- 8. Run the Check syntax → Process window→ Synthesize→ double click check syntax. If any errors found then remove the errors with proper syntax & coding.

- 9. Synthesis your design, from the source window select, synthesis/implementation from the window Now double click the Synthesis -XST.

- 10. After Synthesis, Click on the symbol of FPGA device and Right click and select New Source, Select Implementation Constraints File and type file name and click next.

- 11. Type the Net list and click save.

- 12. Implement the design by double clicking Implement design in the process window.

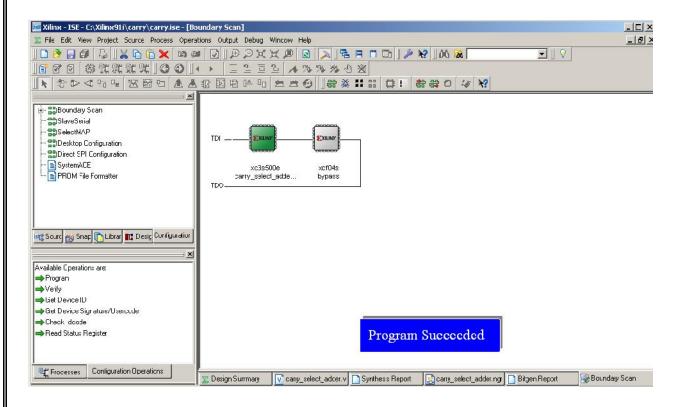

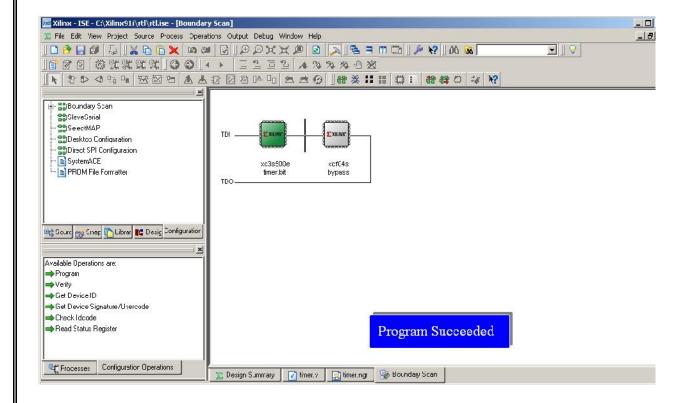

- 13. Then double click Generate Programming File, Double click Configure Target Device and click OK.

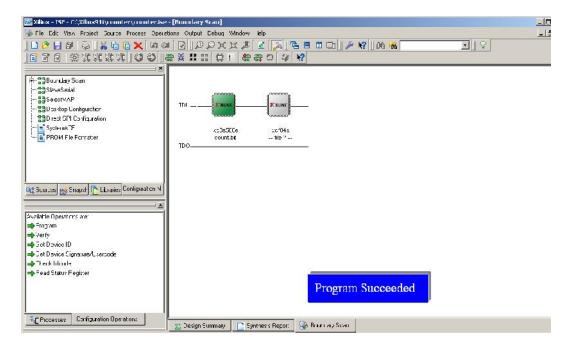

- 14. Double click Create PROM File in the ISE iMPACT window, Select Storage Target Device as Xilinx Flash PROM and click forward.

- 15. Add storage Device as xcf01s [2 M] and click forward, Type Output File Name and Location and click OK.

- 16. Select the corresponding .bit file and click Open, Click No to Add Another Device and Click OK.

- 17. Double click Generate File.

- 18. Double click Boundary Scan and Right click on the window and select Initialize Chain, Now Select the corresponding .mcs file and click open.

- 19. Click OK in the Device Programming Properties window, Download the Program on to the kit by Right clicking on the device icon and select program.

- 20. Verify the output in the target device.

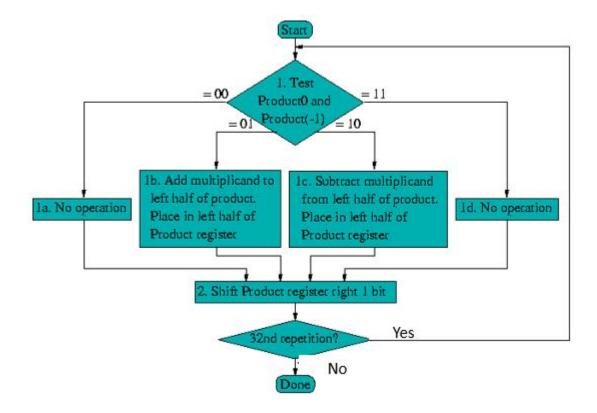

### **BOOTH ALGORITHM:**

### **CODING:**

```

module\ boothmulti(X,\,Y,\,Z);

input signed [3:0] X, Y;

output signed [7:0] Z;

reg signed [7:0] Z;

reg [1:0] temp;

integer i;

reg E1;

reg [3:0] Y1;

always @ (X, Y)

begin

Z = 8'd0;

E1 = 1'd0;

for (i = 0; i < 4; i = i + 1)

begin

temp = \{X[i], E1\};

Y1 = -Y;

case (temp)

2'd2:Z[7:4]=Z[7:4]+Y1;

2'd1 : Z[7:4] = Z[7:4] + Y;

default : begin end

endcase

Z = Z >> 1;

Z[7] = Z[6];

E1 = X[i];

end

if (Y == 4'd8)

begin

Z = -Z;

end

end

endmodule

```

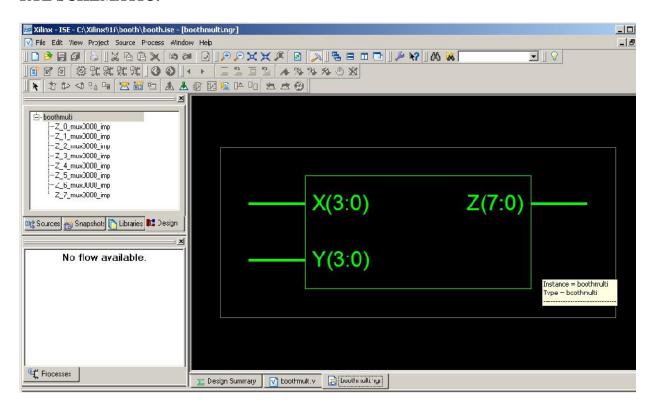

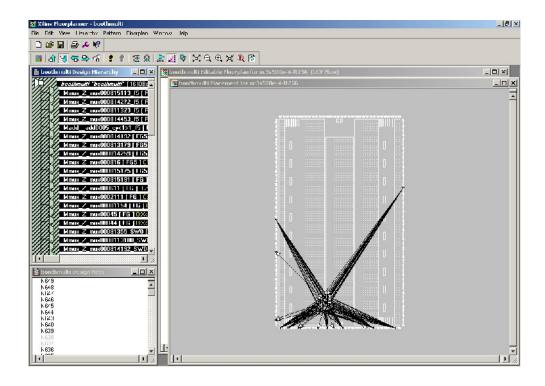

### **RTL SCHEMATIC:**

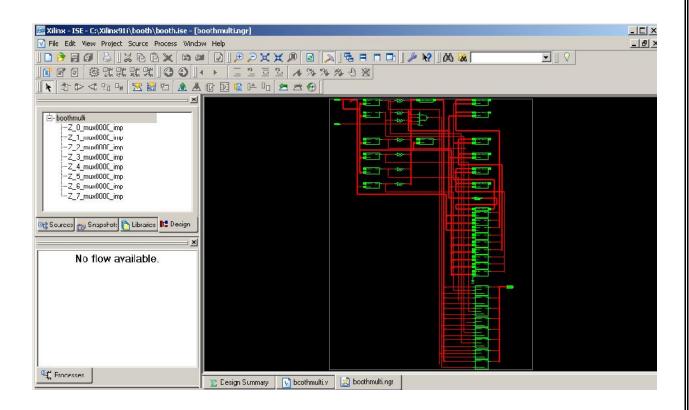

### **TECHNOLOGY SCHEMATIC:**

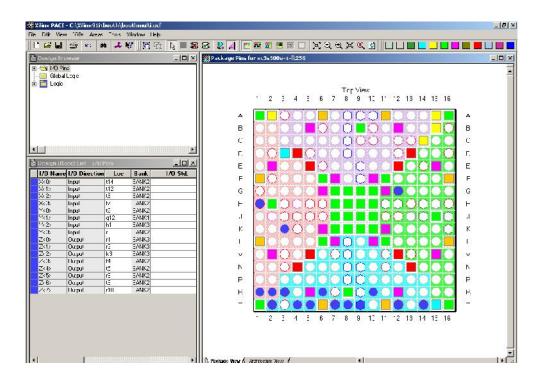

### **PLACE AND ROUTE:**

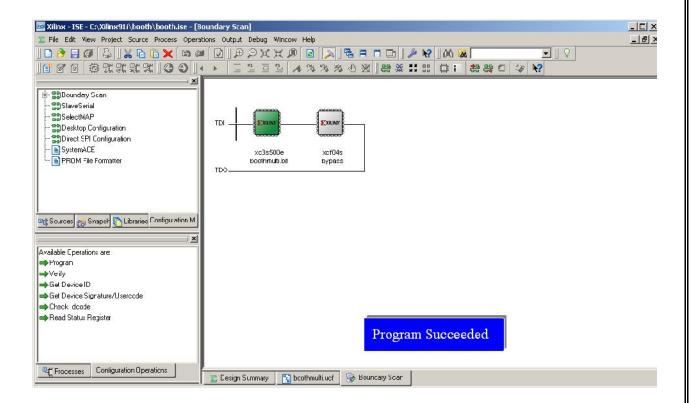

### **HARDWARE FUSING:**

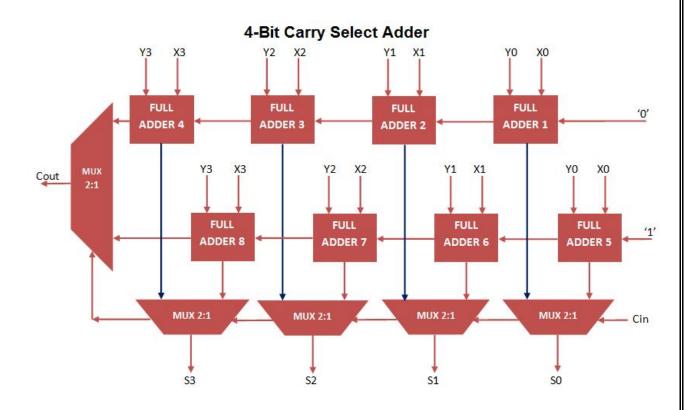

### **CARRY SELECT ADDER:**

### **BLOCK DIAGRAM:**

### **CODING:**

```

module carry_select_adder

( input [3:0] A,B,

input cin,

output [3:0] S,

output cout

);

wire [3:0] temp0,temp1,carry0,carry1;

//for carry 0

fulladder fa00(A[0],B[0],1'b0,temp0[0],carry0[0]);

fulladder fa01(A[1],B[1],carry0[0],temp0[1],carry0[1]);

fulladder fa02(A[2],B[2],carry0[1],temp0[2],carry0[2]);

fulladder fa03(A[3],B[3],carry0[2],temp0[3],carry0[3]);

//for carry 1

fulladder fa10(A[0],B[0],1'b1,temp1[0],carry1[0]);

fulladder fa11(A[1],B[1],carry1[0],temp1[1],carry1[1]);

fulladder fa12(A[2],B[2],carry1[1],temp1[2],carry1[2]);

fulladder fa13(A[3],B[3],carry1[2],temp1[3],carry1[3]);

//mux for carry

multiplexer2 mux_carry(carry0[3],carry1[3],cin,cout);

//mux's for sum

multiplexer2 mux_sum0(temp0[0],temp1[0],cin,S[0]);

multiplexer2 mux_sum1(temp0[1],temp1[1],cin,S[1]);

multiplexer2 mux_sum2(temp0[2],temp1[2],cin,S[2]);

multiplexer2 mux_sum3(temp0[3],temp1[3],cin,S[3]);

endmodule

```

```

module fulladder

( input a,b,cin,

output sum, carry

);

assign sum = a \wedge b \wedge cin;

assign carry = (a & b) | (cin & b) | (a & cin);

endmodule

module multiplexer2

( input i0,i1,sel,

output reg bitout

);

always@(i0,i1,sel)

begin

if(sel == 0)

bitout = i0;

else

bitout = i1;

end

endmodule

```

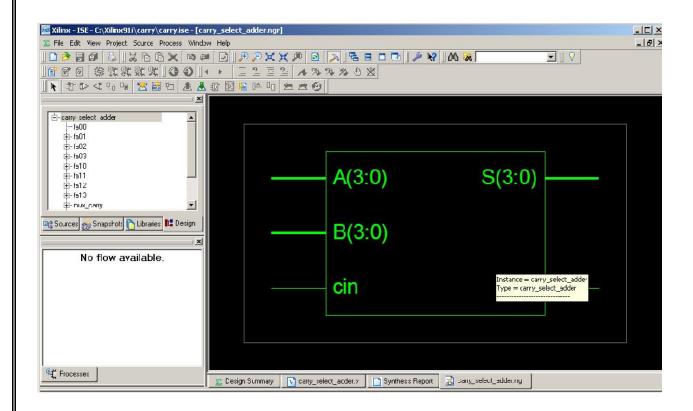

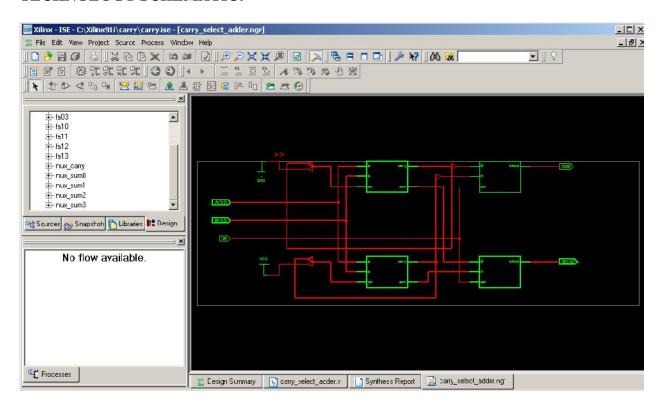

### **RTL SCHEMATIC:**

### **TECHNOLOGY SCHEMATIC:**

### **PLACE AND ROUTE:**

### **HARDWARE FUSING:**

### **RESULT:**

Thus, the Hardware fusing and testing of Booth Multiplier and Carry Select Adder were implemented in Spartan 3E FPGA trainer kit using Xilinx project navigator.

| EXP NO: 4<br>Date: | Design and FPGA Implementation of Sequential Circuits |

|--------------------|-------------------------------------------------------|

|--------------------|-------------------------------------------------------|

### AIM:

To design and implement Counter in FPGA Spartan 3E Trainer kit using Xilinx project navigator.

### **APPARATUS REQUIRED:**

| S.No | S.No Nameofthe equipment/ software |   |

|------|------------------------------------|---|

| 1.   | PC with Windows                    | 1 |

| 2.   | XilinxProject navigator            | 1 |

### **PROCEDURE:**

- 1. Start the Xilinx ISE by using Start  $\rightarrow$  Program files  $\rightarrow$  Xilinx ISE  $\rightarrow$  project navigator

- 2. Click File→ New Project

- 3. Enter the Project Name and select the location then click next

- 4. Select the Device and other category and click next twice and finish.

- 5. Click on the symbol of FPGA device and then right click → click on new source.

- 6. Select the Verilog Module and give the file name →click next and define ports →click next and finish.

- 7. Writing the Verilog Code in Verilog Editor.

- 8. Run the Check syntax → Process window→ Synthesize→ double click check syntax. If any errors found then remove the errors with proper syntax & coding.

- 9. Synthesis your design, from the source window select, synthesis/implementation from the window Now double click the Synthesis -XST.

- 10. After Synthesis, Click on the symbol of FPGA device and Right click and select New Source, Select Implementation Constraints File and type file name and click next.

- 11. Type the Net list and click save.

- 12. Implement the design by double clicking Implement design in the process window.

- 13. Then double click Generate Programming File, Double click Configure Target Device and click OK.

- 14. Double click Create PROM File in the ISE iMPACT window, Select Storage Target Device as Xilinx Flash PROM and click forward.

- 15. Add storage Device as xcf01s [2 M] and click forward, Type Output File Name and Location and click OK.

- 16. Select the corresponding .bit file and click Open, Click No to Add Another Device and Click OK.

- 17. Double click Generate File.

- 18. Double click Boundary Scan and Right click on the window and select Initialize Chain, Now Select the corresponding .mcs file and click open.

- 19. Click OK in the Device Programming Properties window, Download the Program on to the kit by Right clicking on the device icon and select program.

- 20. Verify the output in the target device.

### **CODING:**

```

Module ripple counter (A0, A1, A2, A3, Count, Reset)

Output A0,A1, A2,A3;

Input Count, Reset;

ff f0(A0, Count, Reset);

ff f1(A1, A0, Reset);

ff f2(A2, A1, Reset);

ff f3(A3, A2, Reset);

end module

module ff

(Q, CLK, Reset);

output Q;

input CLK, Reset;

reg Q;

always @ (negedge CLK or negedge Reset)

if (~Reset)

Q=1'b0;

else Q=(\sim Q);

endmodule

```

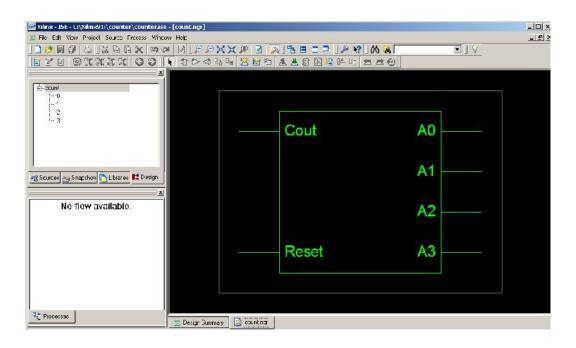

### **RTL SCHEMATIC:**

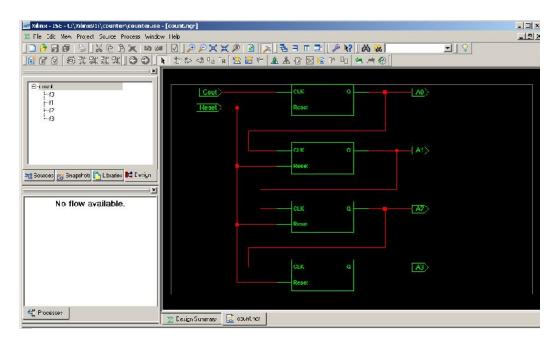

### **TECHNOLOGY SCHEMATIC:**

#### **PLACE AND ROUTE:**

#### HARDWARE FUSING

#### **RESULT:**

Thus, the Hardware fusing and testing of 4-Bit counter was implemented in Spartan 3E FPGA trainer kit using Xilinx project navigator.

#### AIM:

To analyze area, power and delay for Counter and PRBS generator in FPGA Spartan 3E Trainer kit using Xilinx project navigator.

#### **APPARATUS REQUIRED:**

| S.No | Nameofthe equipment/ software | Quantity |

|------|-------------------------------|----------|

| 1.   | PC with Windows               | 1        |

| 2.   | XilinxProject navigator       | 1        |

#### **PROCEDURE:**

- 1. Start the Xilinx ISE by using Start  $\rightarrow$  Program files  $\rightarrow$  Xilinx ISE  $\rightarrow$  project navigator

- 2. Click File→ New Project

- 3. Enter the Project Name and select the location then click next

- 4. Select the Device and other category and click next twice and finish.

- 5. Click on the symbol of FPGA device and then right click → click on new source.

- 6. Select the Verilog Module and give the file name →click next and define ports →click next and finish.

- 7. Writing the Verilog Code in Verilog Editor.

- 8. Run the Check syntax → Process window→ Synthesize→ double click check syntax. If any errors found then remove the errors with proper syntax & coding.

- 9. Synthesis your design, from the source window select, synthesis/implementation from the window Now double click the Synthesis -XST.

- 10. After Synthesis, Click on the synthesis report to generate the area and delay summary.

- 11. Type the Net list and click save.

- 12. Implement the design by double clicking Implement design in the process window.

- 13. Then double click Generate Programming File, Double click Configure Target Device and click OK.

- 14. Double click Create PROM File in the ISE iMPACT window, Select Storage Target Device as Xilinx Flash PROM and click forward.

- 15. Add storage Device as xcf01s [2 M] and click forward, Type Output File Name and Location and click OK.

- 16. Select the corresponding .bit file and click Open, Click No to Add another Device and Click OK.

- 17. Double click Generate File.

- 18. Double click Boundary Scan and Right click on the window and select Initialize Chain, Now Select the corresponding .mcs file and click open.

- 19. Click OK in the Device Programming Properties window, Download the Program on to the kit by Right clicking on the device icon and select program.

- 20. Verify the output in the target device.

#### **RIPPLE COUNTER:**

#### **CODING:**

```

Module ripple counter (A0, A1, A2, A3, Count, Reset)

Output A0,A1, A2,A3;

Input Count, Reset;

ff f0(A0, Count, Reset);

ff f1(A1, A0, Reset);

ff f2(A2, A1, Reset);

ff f3(A3, A2, Reset);

end module

module ff

(Q, CLK, Reset);

output Q;

input CLK, Reset;

reg Q;

always @ (negedge CLK or negedge Reset)

if (~Reset)

Q=1'b0;

else Q=(\sim Q);

endmodule

```

#### **ANALYZE REPORT:**

Area analysis:

### Power analysis:

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 81    |

|                                    |       |       |

| Vccint 1.20V:                      | 26    | 31    |

| Vccaux 2.50V:                      | 18    | 45    |

| Vcco25 2.50V:                      | 2     | 5     |

|                                    |       |       |

| Clocks:                            | 0     | 0     |

| Inputs:                            | 0     | 0     |

| Logic:                             | 0     | 0     |

| Outputs:                           |       |       |

| Vcco25                             | 0     | 0     |

| Signals:                           | 0     | 0     |

|                                    |       |       |

| Quiescent Vccint 1.20V:            | 26    | 31    |

| Quiescent Vccaux 2.50V:            | 18    | 45    |

| Quiescent Vcco25 2.50V:            | 2     | 5     |

| Thermal summary:                |       |

|---------------------------------|-------|

| Estimated junction temperature: | 28C   |

| Ambient temp:                   | 25C   |

| Case temp:                      | 27C   |

| Theta J-A:                      | 31C/W |

### **Delay Analysis:**

Timing Summary:

-----Speed Grade: -4

Minimum period: 2.554ns (Maximum Frequency: 391.543MHz) Minimum input arrival time before clock: No path found Maximum output required time after clock: 4.394ns Maximum combinational path delay: No path found

Timing Detail:

-----

All values displayed in nanoseconds (ns)

\_\_\_\_\_

```

Timing constraint: Default period analysis for Clock 'f2/Q'

Clock period: 2.470ns (frequency: 404.858MHz)

Total number of paths / destination ports: 1 / 1

Delay:

2.470ns (Levels of Logic = 1)

Source:

f3/Q (FF)

Destination:

f3/Q (FF)

Source Clock:

f2/Q falling

Destination Clock: f2/Q falling

Data Path: f3/Q to f3/Q

Gate

Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

FDC_1:C->Q

2 0.591 0.447 f3/Q (f3/Q)

1 0.704 0.420 f3/Q_not00011_INV_0 (f3/Q_not0001) 0.308 f3/Q

INV:I->O

FDC_1:D

Total

2.470ns (1.603ns logic, 0.867ns route)

(64.9% logic, 35.1% route)

______

Timing constraint: Default period analysis for Clock 'f1/Q'

Clock period: 2.554ns (frequency: 391.543MHz)

Total number of paths / destination ports: 1 / 1

Delay:

2.554ns (Levels of Logic = 1)

Source:

f2/Q (FF)

Destination:

f2/Q (FF)

Source Clock:

f1/Q falling

Destination Clock: f1/Q falling

Data Path: f2/Q to f2/Q

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

-----

FDC_1:C->Q 3 0.591 0.531 f2/Q (f2/Q)

INV:I->O

FDC_1:D

1 0.704 0.420 f2/Q not00011 INV 0 (f2/Q not0001)

0.308

FDC_1:D

f2/O

2.554ns (1.603ns logic, 0.951ns route)

Total

(62.8% logic, 37.2% route)

Timing constraint: Default period analysis for Clock 'f0/Q'

Clock period: 2.554ns (frequency: 391.543MHz)

Total number of paths / destination ports: 1 / 1

_____

Delay:

2.554ns (Levels of Logic = 1)

f1/O (FF)

Source:

f1/Q (FF)

Destination:

Source Clock: f0/Q falling

Destination Clock: f0/Q falling

Data Path: f1/Q to f1/Q

Gate

Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

FDC_1:C->Q

3 0.591 0.531 f1/O (f1/O)

1 0.704 0.420 f1/Q_not00011_INV_0 (f1/Q_not0001) 0.308 f1/Q

INV:I->O

FDC_1:D

Total

2.554ns (1.603ns logic, 0.951ns route)

(62.8% logic, 37.2% route)

```

```

Timing constraint: Default period analysis for Clock 'Cout'

Clock period: 2.554ns (frequency: 391.543MHz)

Total number of paths / destination ports: 1 / 1

Delay:

2.554ns (Levels of Logic = 1)

Source:

f0/Q (FF)

Destination:

f0/Q (FF)

Source Clock:

Cout falling

Destination Clock: Cout falling

Data Path: f0/Q to f0/Q

Gate

Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

FDC_1:C->Q

3 0.591 0.531 f0/Q (f0/Q)

1 0.704 0.420 f0/Q_not00011_INV_0 (f0/Q_not0001) 0.308 f0/Q

INV:I->O

FDC_1:D

Total

2.554ns (1.603ns logic, 0.951ns route)

(62.8% logic, 37.2% route)

Timing constraint: Default OFFSET OUT AFTER for Clock 'Cout'

Total number of paths / destination ports: 1 / 1

Offset:

4.394ns (Levels of Logic = 1)

Source:

f0/Q (FF)

A0 (PAD)

Destination:

Source Clock: Cout falling

Data Path: f0/Q to A0

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

-----

FDC_1:C->Q 3 0.591 0.531 f0/Q (f0/Q)

OBUE-L->Q 3 272 A0 OBUE (A0)

OBUF:I->O

3.272

A0 OBUF (A0)

4.394ns (3.863ns logic, 0.531ns route)

Total

(87.9% logic, 12.1% route)

_____

Timing constraint: Default OFFSET OUT AFTER for Clock 'f0/Q'

Total number of paths / destination ports: 1 / 1

_____

Offset:

4.394ns (Levels of Logic = 1)

Source:

f1/Q (FF)

Destination:

A1 (PAD)

Source Clock:

f0/Q falling

Data Path: f1/Q to A1

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

FDC_1:C->Q 3 0.591 0.531 f1/Q (f1/Q)

OBUF:I->O

3.272

A1_OBUF(A1)

4.394ns (3.863ns logic, 0.531ns route)

(87.9% logic, 12.1% route)

```

Timing constraint: Default OFFSET OUT AFTER for Clock 'f1/Q'

Total number of paths / destination ports: 1 / 1

\_\_\_\_\_

Offset: 4.394ns (Levels of Logic = 1)

Source: f2/Q (FF)

Destination: A2 (PAD)

Source Clock: f1/Q falling

Data Path: f2/Q to A2

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

EDC 1.C > 0 2 0.501 0.521 f2/0.

FDC\_1:C->Q 3 0.591 0.531 f2/Q (f2/Q) OBUF:I->O 3.272 A2\_OBUF (A2)

-----

Total 4.394ns (3.863ns logic, 0.531ns route)

(87.9% logic, 12.1% route)

\_\_\_\_\_\_

Timing constraint: Default OFFSET OUT AFTER for Clock 'f2/Q'

Total number of paths / destination ports: 1 / 1

-----

Offset: 4.310ns (Levels of Logic = 1)

Source: f3/Q (FF)

Destination: A3 (PAD)

Source Clock: f2/Q falling

Data Path: f3/Q to A3

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

-----

FDC\_1:C->Q 2 0.591 0.447 f3/Q (f3/Q) OBUF:I->O 3.272 A3\_OBUF (A3)

-----

Total 4.310ns (3.863ns logic, 0.447ns route)

(89.6% logic, 10.4% route)

\_\_\_\_\_

CPU : 3.91 / 4.03 s | Elapsed : 4.00 / 4.00 s

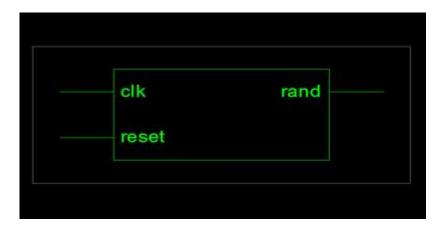

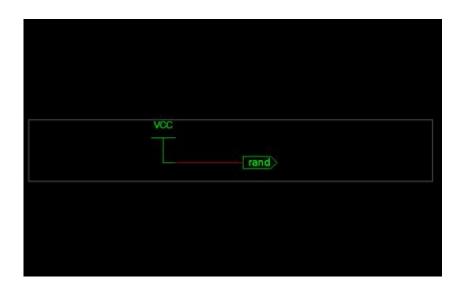

#### PRBS GENERATOR:

#### **CODING:**

```

module prbs1 (rand, clk, reset);

input clk, reset;

output rand;

wire rand;

reg [3:0] temp;

always @ (posedge reset) begin

temp <= 4'hf;

end

always @ (posedge clk) begin

if (~reset) begin

temp <= {temp[0]^temp[1],temp[3],temp[2],temp[1]};

end

end

assign rand = temp[0];

endmodule</pre>

```

#### **RTL SCEMATIC:**

#### **TECHNOLOGY SCHEMATIC:**

# **REPORT:**

| <b>A</b> | A 1  |          |

|----------|------|----------|

| A roo    | Ano  | TICIC.   |

| Area     | Alla | 1 V 515. |

|          |      | .,       |

| Device utilization summary: |          |      |    |

|-----------------------------|----------|------|----|

| Selected Device: 3s500eft25 | 6-4      |      |    |

| Number of Slices:           | 0 out of | 4656 | 0% |

| Number of IOs:              | 3        |      |    |

| Number of bonded IOBs:      | 1 out of | 190  | 0% |

| Partition Resource Summary  | -        |      |    |

|                             |          |      |    |

No Partitions were found in this design.

# **Power Analysis:**

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 81    |

|                                    |       |       |

| <b>Vccint 1.20V:</b>               | 26    | 31    |

| Vccaux 2.50V:                      | 18    | 45    |

| Vcco25 2.50V:                      | 2     | 5     |

| Inputs:                            | 0     | 0     |

| Outputs:                           |       |       |

| Vcco25                             | 0     | 0     |

| Signals:                           | 0     | 0     |

| Quiescent Vccint 1.20V:            | 26    | 31    |

| Quiescent Vccaux 2.50V:            | 18    | 45    |

| Quiescent Vcco25 2.50V:            | 2     | 5     |

| Thermal summary:                |       |

|---------------------------------|-------|

| Estimated junction temperature: | 28C   |

| Ambient temp:                   | 25C   |

| Case temp:                      | 27C   |

| Theta J-A:                      | 31C/W |

#### **Delay Analysis:**

#### TIMING REPORT

NOTE: THESE TIMING NUMBERS ARE ONLY A SYNTHESIS ESTIMATE.

FOR ACCURATE TIMING INFORMATION PLEASE REFER TO THE TRACE REPORT GENERATED AFTER PLACE-and-ROUTE.

#### Clock Information:

No clock signals found in this design

Asynchronous Control Signals Information:

No asynchronous control signals found in this design

#### Timing Summary:

\_\_\_\_

Speed Grade: -4

Minimum period: No path found

Minimum input arrival time before clock: No path found Maximum output required time after clock: No path found Maximum combinational path delay: No path found

#### Timing Detail:

\_\_\_\_\_

All values displayed in nanoseconds (ns)

CPU: 3.84 / 4.19 s | Elapsed: 4.00 / 4.00 s

#### **RESULT:**

Thus, area, power and delay for Counter and PRBS generator was analyzed in FPGA Spartan 3E Trainer kit using Xilinx project navigator.

| EXP NO: 6 | To all DITA and A Deal Trian Class        |

|-----------|-------------------------------------------|

| EAI NO. 0 | Invoke PLL to generate Real Time Clock    |

| Date:     | invoke i zz to generate itear i mie cioen |

| Date:     |                                           |

#### AIM:

To invoke the FPGA Spartan 3E PLL to generate Real time Clock kit using Xilinx project navigator.

#### **APPARATUS REQUIRED:**

| S.No | Nameofthe equipment/ software | Quantity |

|------|-------------------------------|----------|

| 1.   | PC with Windows               | 1        |

| 2.   | XilinxProject navigator       | 1        |

#### **PROCEDURE:**

- 1. Start the Xilinx ISE by using Start  $\rightarrow$  Program files  $\rightarrow$  Xilinx ISE  $\rightarrow$  project navigator

- 2. Click File→ New Project

- 3. Enter the Project Name and select the location then click next

- 4. Select the Device and other category and click next twice and finish.

- 5. Click on the symbol of FPGA device and then right click → click on new source.

- 6. Select the Verilog Module and give the file name →click next and define ports →click next and finish.

- 7. Writing the Verilog Code in Verilog Editor.

- 8. Run the Check syntax → Process window→ Synthesize→ double click check syntax. If any errors found then remove the errors with proper syntax & coding.

- 9. Synthesis your design, from the source window select, synthesis/implementation from the window Now double click the Synthesis -XST.

- 10. After Synthesis, Click on the symbol of FPGA device and Right click and select New Source, Select Implementation Constraints File and type file name and click next.

- 11. Type the Net list and click save.

- 12. Implement the design by double clicking Implement design in the process window.

- 13. Then double click Generate Programming File, Double click Configure Target Device and click OK.

- 14. Double click Create PROM File in the ISE iMPACT window, Select Storage Target Device as Xilinx Flash PROM and click forward.

- 15. Add storage Device as xcf01s [2 M] and click forward, Type Output File Name and Location and click OK.

- 16. Select the corresponding .bit file and click Open, Click No to Add Another Device and Click OK

- 17. Double click Generate File.

- 18. Double click Boundary Scan and Right click on the window and select Initialize Chain, Now Select the corresponding .mcs file and click open.

- 19. Click OK in the Device Programming Properties window, Download the Program on to the kit by Right clicking on the device icon and select program.

- 20. Verify the output in the target device.

**FPGA** Connections to Seven-Segment Display

| SEGMENT | FPGA PIN |

|---------|----------|

| A       | P8       |

| В       | P10      |

| С       | P9       |

| D       | P6       |

| Е       | P4       |

| F       | P5       |

| G       | Р3       |

| DP      | P11      |

#### **CLOCK SOURCE**

Spartan3E FPGA works in different Clock frequencies

| Clock Input | FPGA PIN |  |  |

|-------------|----------|--|--|

| CLK         | A8       |  |  |

| RST         | J6       |  |  |

#### **Digit Enable Signals**

| Display  | DISP 1 | DISP 2 | DISP 3 | DISP 4 | DISP 5 | DISP 6 |

|----------|--------|--------|--------|--------|--------|--------|

| FPGA PIN | P1     | P2     | P7     | R4     | R11    | N14    |

#### PLL OSCILLATOR SETTINGS

For PLL, ICS525-01 or ICS525-02 is used. Select the clock settings as per the PLL in the On board 0 = Shorted

1 = Open

For any other CLK frequency in between 1MHz to 100MHz use the following formula.

CLK frequency = Input frequency

$$*$$

2

$$\frac{(VDW + 8)}{(RDW + 2)(OD)}$$

Where,

Reference Divider Word (RDW) = 1 to 127 (0 is not permitted) VCO Divider Word (VDW) = 4 to 511 (0, 1, 2, 3 are not permitted)

Output Divider (OD) = values below

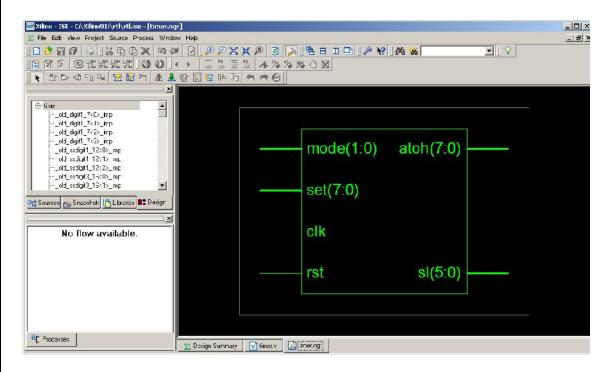

#### **CODING:**

```

System Clock = 20MHz

Verilog Program

// System clock Frequency 20MHz

// MODE Functions

// 00 HOURS

// 01 Minutes

// 10 Seconds

// 11 Timer ON

module timer(clk, rst, mode, set, sl, atoh);

input clk; // System Clock

input rst; // Reset(micro switch)

input [1:0] mode; // Mode Selection(switch 1 & switch 2)

input [7:0] set; // Set Value(switch 4 to switch 11)

output [5:0] sl; // Segment Selection

output [7:0] atoh; // Segment Display Control Data

reg [5:0] sl;

reg [7:0] atoh;

reg [26:0] sig2;

reg [19:1] sig3;

reg [7:0] ssdigit1;

reg [7:0] ssdigit2;

reg [7:0] ssdigit3;

reg [7:0] ssdigit4;

reg [7:0] ssdigit5;

reg [7:0] ssdigit6;

reg [3:0] digit1;

reg [3:0] digit2;

reg [3:0] digit3;

reg [3:0] digit4;

reg [3:0] digit5;

reg [3:0] digit6;

always @ (posedge clk or negedge rst)

begin

if (rst == 1'b0) begin

sig2 = 0;

sig3 = 0;

digit1 = 0;

digit2 = 0;

digit3 = 0;

digit4 = 0;

digit5 = 0;

digit6 = 0;

end

```

```

else begin

if (mode == 2'b00) begin // Hours

if (set[7:4] <= 4'b0001) begin

digit1 = set[7:4];

if (set[3:0] \le 4b1001)

digit2 = set[3:0];

else

digit2 = 0;

end

else if (set[7:4] == 4'b0010) begin

if (set[3:0] \le 4b0011) begin

digit1 = set[7:4];

digit2 = set[3:0];

end

else begin

digit1 = 0;

digit2 = 0;

end

end

else begin

digit1 = 0;

digit2 = 0;

end

end

else if (mode == 2'b01) begin // Minutes

if (set[7:4] <= 4'b0101) begin

digit3 = set[7:4];

if (set[3:0] \le 4b1001)

digit4 = set[3:0];

else

digit4 = 0;

end

else begin

digit3 = 0;

digit4 = 0;

end

end

else if (mode == 2'b10) begin // Seconds

if (set[7:4] \le 4'b0101) begin

digit5 = set[7:4];

if (set[3:0] \le 4b1001)

digit6 = set[3:0];

else

digit6 = 0;

end

else begin

digit5 = 0;

digit6 = 0;

end

end

```

```

else begin

sig2 = sig2 + 1;

case (sig2[24:23]) //RTC Function

2'b00 : begin

digit6 = digit6 + 1;

if (digit6 > 4'b1001) begin

digit6 = 4'b0000;

digit5 = digit5 + 1;

if (digit5 > 4'b0101) begin

digit5 = 4'b0000;

digit4 = digit4 + 1;

if (digit4 > 4'b1001) begin

digit4 = 4'b0000;

digit3 = digit3 + 1;

if (digit3 > 4'b0101) begin

digit3 = 4'b0000;

digit2 = digit2 + 1;

if (digit2 > 4'b1001) begin

digit2 = 4'b0000;

digit1 = digit1 + 1;

end

if ((digit1 >= 4'b0010) & (digit2 >= 4'b0100))

begin

digit1 = 4'b0000;

digit2 = 4'b0000;

end

end

end

end

end

sig2[24:23] = 2'b01;

end

2'b11 : begin

if (sig2[22:19] == 4'b1001)

sig2 = 0;

end

default: begin

end

endcase

end

```

```

Display Settings

sig3 = sig3 + 1;

case (sig3[17:15])

3'b000 : begin

sl = 6'b1111110;

case (digit1)

4'b0000 : ssdigit1 = 8'b00111111;

4'b0001 : ssdigit1 = 8'b00000110;

4'b0010 : ssdigit1 = 8'b01011011;

default : ssdigit1 = 8'b000000000;

endcase

atoh = ssdigit1;

end

3'b001 : begin

sl = 6'b111101;

case (digit2)

4'b0000 : ssdigit2 = 8'b001111111;

4'b0001 : ssdigit2 = 8'b00000110;

4'b0010 : ssdigit2 = 8'b01011011;

4'b0011 : ssdigit2 = 8'b01001111;

4'b0100 : ssdigit2 = 8'b01100110;

4'b0101 : ssdigit2 = 8'b01101101;

4'b0110 : ssdigit2 = 8'b01111101;

4'b0111 : ssdigit2 = 8'b00000111;

4'b1000 : ssdigit2 = 8'b011111111;

4'b1001 : ssdigit2 = 8'b01101111;

default: ssdigit2 = 8'b000000000;

endcase

atoh = ssdigit2;

end

3'b011 : begin

sl = 6'b111011;

case (digit3)

4'b0000 : ssdigit3 = 8'b001111111;

4'b0001 : ssdigit3 = 8'b00000110;

4'b0010 : ssdigit3 = 8'b01011011;

4'b0011 : ssdigit3 = 8'b01001111;

4'b0100 : ssdigit3 = 8'b01100110;

4'b0101 : ssdigit3 = 8'b01101101;

default : ssdigit3 = 8'b000000000

endcase

atoh = ssdigit3;

end

3'b100 : begin

sl = 6'b110111;

case (digit4)

4'b0000 : ssdigit4 = 8'b00111111;

4'b0001 : ssdigit4 = 8'b00000110;

4'b0010 : ssdigit4 = 8'b01011011;

```

```

4'b0011 : ssdigit4 = 8'b01001111;

4'b0100 : ssdigit4 = 8'b01100110;

4'b0101 : ssdigit4 = 8'b01101101;

4'b0110 : ssdigit4 = 8'b01111101;

4'b0111 : ssdigit4 = 8'b00000111;

4'b1000 : ssdigit4 = 8'b01111111;

4'b1001 : ssdigit4 = 8'b01101111;

default : ssdigit4 = 8'b000000000;

endcase

atoh = ssdigit4;

end

3'b110 : begin

sl = 6'b1011111;

case (digit5)

4'b0000 : ssdigit5 = 8'b00111111;

4'b0001 : ssdigit5 = 8'b00000110;

4'b0010 : ssdigit5 = 8'b01011011;

4'b0011 : ssdigit5 = 8'b01001111;

4'b0100 : ssdigit5 = 8'b01100110;

4'b0101 : ssdigit5 = 8'b01101101;

default : ssdigit5 = 8'b000000000;

endcase

atoh = ssdigit5;

end

3'b111 : begin

sl = 6'b0111111;

case (digit6)

4'b0000 : ssdigit6 = 8'b00111111;

4'b0001 : ssdigit6 = 8'b00000110;

4'b0010 : ssdigit6 = 8'b01011011;

4'b0011 : ssdigit6 = 8'b01001111;

4'b0100 : ssdigit6 = 8'b01100110;

4'b0101 : ssdigit6 = 8'b01101101;

4'b0110 : ssdigit6 = 8'b01111101;

4'b0111 : ssdigit6 = 8'b00000111;

4'b1000 : ssdigit6 = 8'b011111111;

4'b1001 : ssdigit6 = 8'b01101111;

default : ssdigit6 = 8'b000000000;

endcase

atoh = ssdigit6;

end

endcase

end

end

endmodule

```

#### **RTL SCHEMATIC**

#### TECHNOLOGY SCHEMATIC

#### HARDWARE FUSING

#### **RESULT:**

Thus, the FPGA Spartan 3E PLL was invoked to generate Real time Clock in kit using Xilinx project navigator.

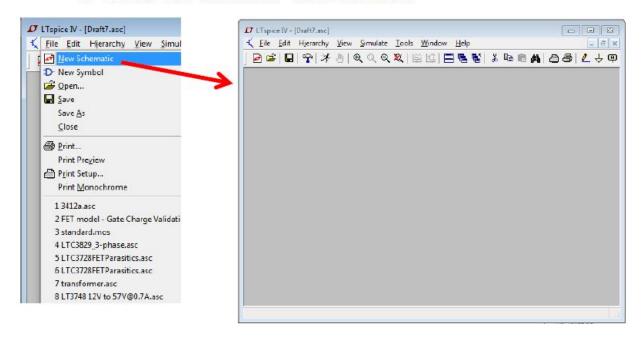

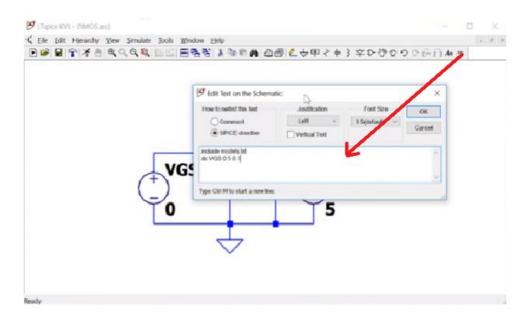

# LT SPICE Procedure for simulationandimplementation of EDA tool-LtSPICE

- Step 1: Open up a blank schematic screen

- Select "File" Menu and "New Schematic"

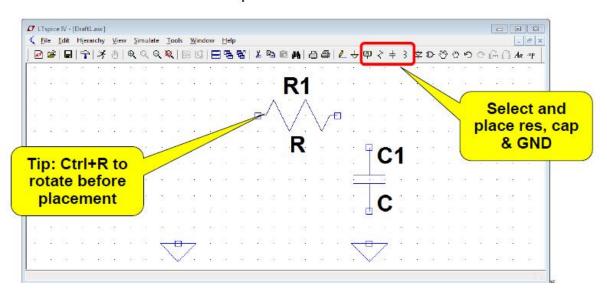

- Step 2: Add the passives and grounds

- Using the toolbar, select Resistor, Capacitor and Ground.

Place these symbols on the schematic as shown below. Use Ctrl+R to rotate before placement.

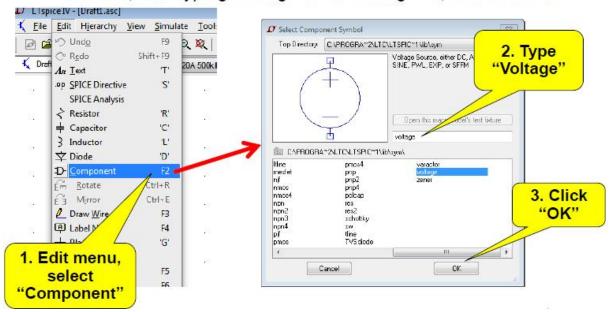

### Step 3: Add the voltage source

Select "Edit" Menu and "Component". From the component window, start typing "voltage" in the dialog box, and click "OK"

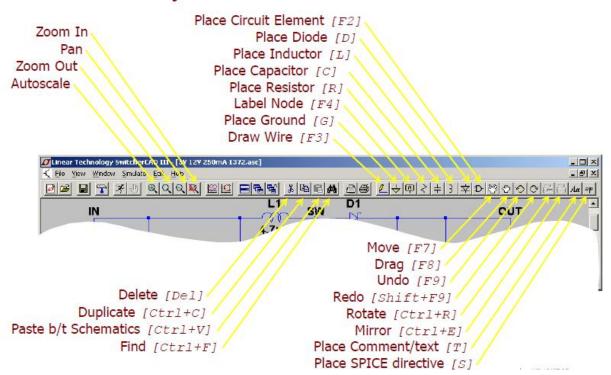

# Toolbar and Keyboard Shortcuts

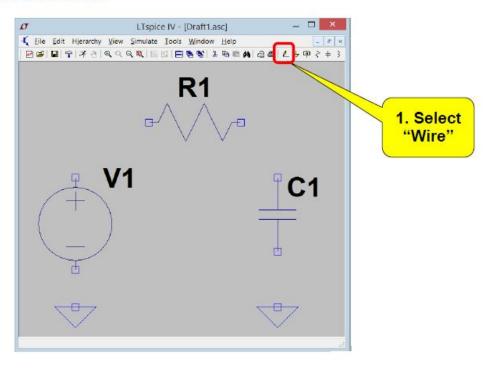

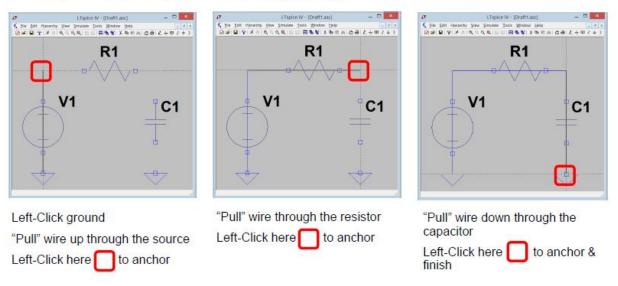

# Step 4: Wire up the circuit

· Using the toolbar, select Wire

# Step 4: Wire up the circuit (cont.)

Hint: Press the ESC key at any time to clean up the schematic

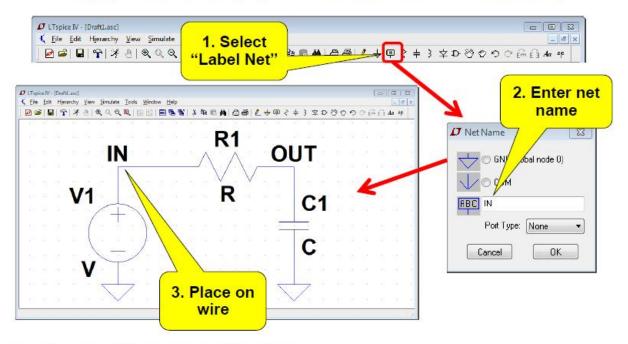

# Step 5: Add net labels

Using the toolbar, select Label Net. Label the input/output nodes as shown below

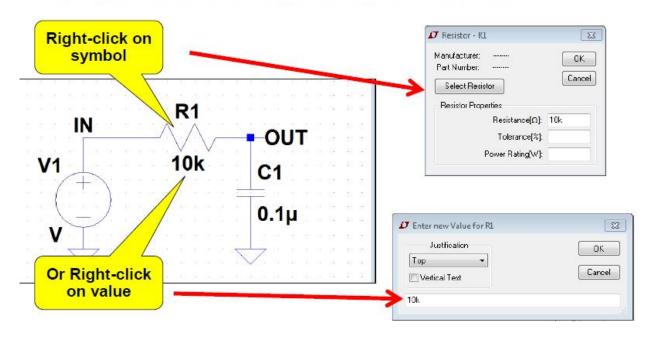

## Step 6a: Component values

\* Right-Click on each component symbol to change its value as shown below

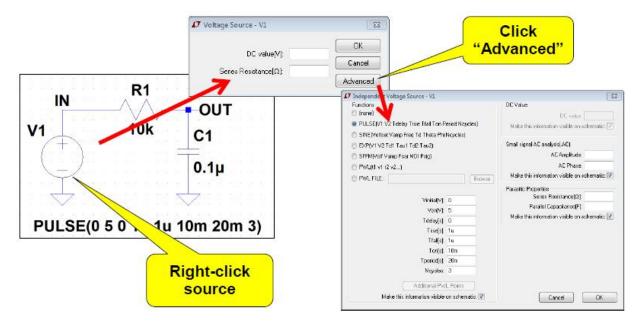

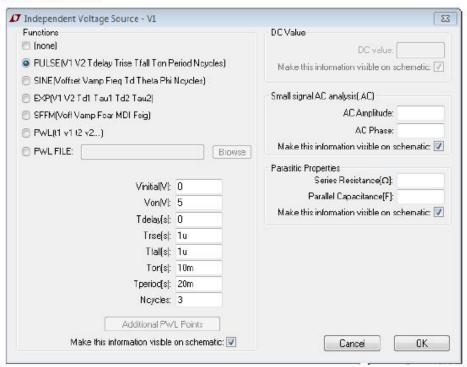

# Step 6b: Source parameters

Right-Click on the voltage source and enter the parameters shown below under the "Advanced" tab.

# Step 6b: Source parameters

Right-Click on the voltage source and enter the parameters shown below under the "Advanced" tab.

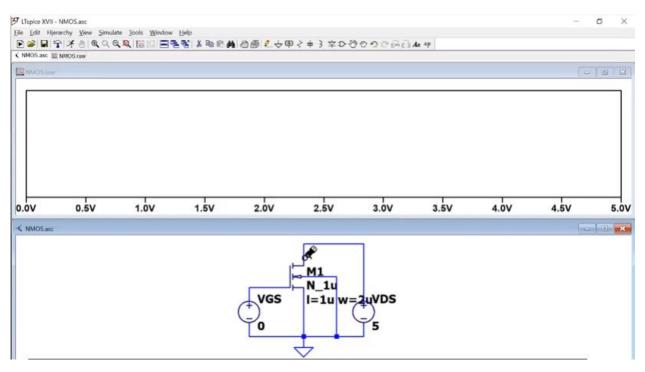

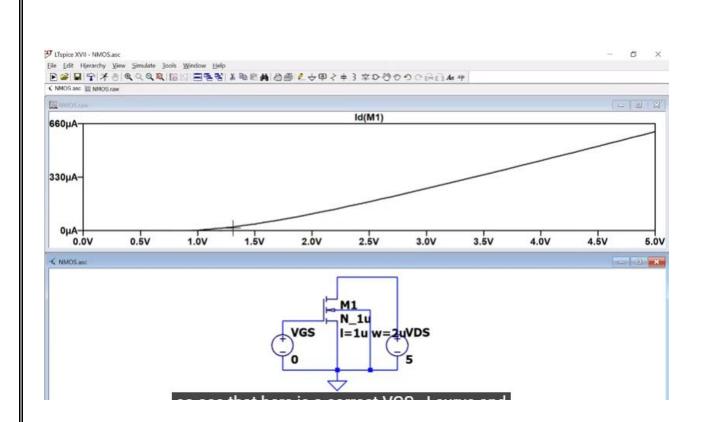

### DC Sweep

• Run the Simulation for Transient Response

- Add pane to output

- Right click -> add new pane

- · Viewing Differential Voltage Waveforms

- Left-Click on one node and drag the mouse to another node

- Red voltage probe at the first node

- Black probe on the second

#### TRANSISTOR MODELS

\* Long channel models from CMOS Circuit Design, Layout, and Simulation, \* Level=3 models VDD=5V, see CMOSedu.com

\*

#### .MODEL $N_1u$ NMOS LEVEL = 3

\*

### .MODEL $P_1u$ PMOS LEVEL = 3

\*

\*

\*

.model N\_50n nmos level = 54 +binunit = 1 paramchk= 1 mobmod = 0

<sup>\*</sup> Short channel models from CMOS Circuit Design, Layout, and Simulation,

<sup>\* 50</sup>nm BSIM4 models VDD=1V, see CMOSedu.com

```

+capmod = 2

igcmod = 1

igbmod = 1

geomod = 0

+diomod = 1

rdsmod = 0

rbodymod= 1

rgatemod= 1

+permod = 1

acnqsmod= 0

trnqsmod = 0

toxe = 1.4e-009

+tnom = 27

toxp = 7e-010

toxm = 1.4e-009

wint = 5e-009

+epsrox = 3.9

lint = 1.2e-008

+ll

=0

wl

= 0

lln

= 1

wln = 1

+lw

=0

=0

ww

lwn

= 1

wwn = 1

+lwl

xpart = 0

toxref = 1.4e-009

=0

wwl = 0

+vth0 = 0.22

= 0.35

k1

k2

= 0.05

k3

= 0

=0

= 2.5e-006

dvt0 = 2.8

+k3b

w0

dvt1 = 0.52

+dvt2 = -0.032

dvt0w = 0

dvt1w = 0

dvt2w = 0

+dsub = 2

minv = 0.05

voffl = 0

dvtp0 = 1e-007

lpe0 = 5.75e-008 lpeb = 2.3e-010

+dvtp1 = 0.05

хj

= 2e-008

+ngate = 5e+020

ndep = 2.8e + 0.18

nsd = 1e + 020

phin = 0

+cdsc = 0.0002

cdscb = 0

cdscd = 0

cit

=0

+voff = -0.15

nfactor = 1.2

eta0 = 0.15

etab = 0

= -0.55

u0

= 0.032

= 1.6e-010

= 1.1e-017

+vfb

ub

ua

= -3e-011

vsat = 1.1e+005

= 1e-020

a0

=2

ags

=0

a2

= 1

b0

= -1e-020

=0

+a1

b1

dwb

pclm = 0.18

+keta = 0.04

dwg

=0

= 0

pdiblcb = -0.005

+pdiblc1 = 0.028

pdiblc2 = 0.022

drout = 0.45

pscbe2 = 1e-007

+pvag = 1e-020

delta = 0.01

pscbe1 = 8.14e+008

+fprout = 0.2

pdits = 0.2

pditsd = 0.23

pditsl = 2.3e + 006

rdw = 150

rdsw = 150

+rsh

=3

rsw

= 150

rswmin = 0

+rdswmin = 0

rdwmin = 0

prwg = 0

+prwb = 6.8e-011

= 1

alpha0 = 0.074

alpha1 = 0.005

wr

bgid1 = 2.1e+009

+beta0 = 30

agidl = 0.0002

cgidl = 0.0002

+egidl = 0.8

+aigbacc = 0.012

bigbacc = 0.0028

cigbacc = 0.002

+nigbacc = 1

aigbinv = 0.014

bigbinv = 0.004

cigbinv = 0.004

+eigbinv = 1.1

nigbinv = 3

aigc = 0.017

bigc = 0.0028

+cigc = 0.002

aigsd = 0.017

bigsd = 0.0028

cigsd = 0.002

+nigc = 1

poxedge = 1

pigcd = 1

ntox = 1

+xrcrg1 = 12

xrcrg2 = 5

```

```

+cgso = 6.238e-010 cgdo = 6.238e-010 cgbo = 2.56e-011

cgdl = 2.495e-10

+cgsl = 2.495e-10 ckappas = 0.02

ckappad = 0.02

acde = 1

noff = 0.9

+moin = 15

voffcv = 0.02

+kt1

= -0.21

kt11 = 0.0

kt2

= -0.042

ute = -1.5

= 1e-009

ub1

= -3.5e-019

uc1 = 0

prt = 0

+ua1

= 53000

+at

+fnoimod = 1

tnoimod = 0

= 0.0001

jswgs = 1e-010

+iss

jsws = 1e-011

njs

= 1

+ijthsfwd = 0.01

ijthsrev=0.001

bvs = 10

xibvs = 1

= 0.0001

jswd = 1e-011

jswgd = 1e-010

+jsd

njd

= 1

+ijthdfwd=0.01

bvd = 10

ijthdrev=0.001

xjbvd = 1

+pbs = 1

cis = 0.0005

mis = 0.5

pbsws = 1

+cisws = 5e-010

mjsws = 0.33

pbswgs = 1

ciswgs = 5e-010

pbd = 1

+mjswgs = 0.33

cid = 0.0005

mjd = 0.5

ciswd = 5e-010

mjswd = 0.33

+pbswd = 1

pbswgd = 1

+cjswgd = 5e-010

mjswgd = 0.33

tpb

= 0.005

tci

= 0.001

tpbswg = 0.005

+tposw = 0.005

tc_1sw = 0.001

tcjswg = 0.001

```

```

+xtis = 3

xtid = 3

dmdg = 0e-006

dmci = 0e-006

+dmcg = 0e-006

dmcgt = 0e-007

+dwj

= 0e-008

= 0e-007 xg1 = 0e-008

xgw

+rshg = 0.4

gbmin = 1e-010

rbpb = 5

rbpd = 15

+rbps = 15

rbdb = 15

rbsb = 15

ngcon = 1

.model P_50n pmos level = 54

paramchk= 1

+binunit = 1

mobmod = 0

geomod = 0

+capmod = 2

igcmod = 1

igbmod = 1

+diomod = 1

rdsmod = 0

rbodymod= 1

rgatemod= 1

+permod = 1

acnqsmod= 0

trnqsmod=0

toxe = 1.4e-009

toxp = 7e-010

+tnom = 27

toxm = 1.4e-009

wint = 5e-009 lint = 1.2e-008

+epsrox = 3.9

=0

wl

=0

lln

= 1

wln

+ll

lwn = 1

+lw

=0

=0

wwn = 1

WW

toxref = 1.4e-009

wwl = 0

+lwl = 0

xpart = 0

= 0.39

+vth0 = -0.22

k1

k2

= 0.05

k3

=0

w0

= 2.5e-006

dvt0 = 3.9

dvt1 = 0.635

+dvt2 = -0.032

dvt0w = 0

dvt1w = 0

dvt2w = 0

voffl = 0

+dsub = 0.7

minv = 0.05

dvtp0 = 0.5e-008

+dvtp1 = 0.05

lpe0 = 5.75e-008 lpeb = 2.3e-010 xj = 2e-008

ndep = 2.8e + 0.18 \quad nsd = 1e + 0.20

+ngate = 5e+020

phin = 0

cit = 0

cdscb = 0

cdscd = 6.1e-008

+cdsc = 0.000258

+voff = -0.15

nfactor = 2

eta0 = 0.15

etab = 0

+vfb = 0.55

=0.0095

= 1.6e-009

u0

ua

ub

= 8e-018

= 4.6e-013

vsat = 90000

a0

= 1.2

= 1e-020

+uc

ags

=0

a2

b0

= -1e-020

=0

+a1

= 1

b1

+keta = -0.047

dwg = 0

dwb = 0

pclm = 0.55

+pdiblc1 = 0.03

pdiblc2 = 0.0055

pdibleb = 3.4e-008 drout = 0.56

+pvag = 1e-020

delta = 0.014

pscbe1 = 8.14e+008 \quad pscbe2 = 9.58e-007

pditsd = 0.23

+fprout = 0.2

pdits = 0.2

pdits1 = 2.3e + 006

+rsh = 3

rdsw = 250

rsw = 160

rdw

= 160

+rdswmin = 0

rdwmin = 0

rswmin = 0

prwg = 3.22e-008

+prwb = 6.8e-011

alpha0 = 0.074

alpha1 = 0.005

wr

= 1

+beta0 = 30

agid1 = 0.0002

bgidl = 2.1e+009 cgidl = 0.0002

+egidl = 0.8

+aigbacc = 0.012

bigbacc = 0.0028

cigbacc = 0.002

aigbinv = 0.014

bigbinv = 0.004

+nigbacc = 1

cigbinv = 0.004

+eigbinv = 1.1

nigbinv = 3

aigc = 0.69

bigc = 0.0012

+cigc = 0.0008

aigsd = 0.0087

bigsd = 0.0012

cigsd = 0.0008

+nigc = 1

poxedge = 1

pigcd = 1

ntox = 1

+xrcrg1 = 12

xrcrg2 = 5

+cgso = 7.43e-010 cgdo = 7.43e-010 cgbo = 2.56e-011 cgdl = 1e-014

ckappas = 0.5

ckappad = 0.5

acde = 1

+cgsl = 1e-014

+moin = 15

noff = 0.9

voffcv = 0.02

= -0.19

kt11 = 0

kt2

= -0.052

ute = -1.5

+kt1

= 2e-018

uc1 = 0

+ua1

= -1e-009

ub1

prt = 0

+at

= 33000

tnoimod = 0

+fnoimod = 1

jswgs = 1e-010

= 0.0001

jsws = 1e-011

+iss

njs

+1]tnsIwa= 0.01

1]tnsrev= 0.001

DVS = 10

X | DVS = I

```

```

+jsd = 0.0001

jswd = 1e-011

jswgd = 1e-010

nid = 1

ijthdrev = 0.001

bvd = 10

+ijthdfwd=0.01

xjbvd = 1

+pbs = 1

cis = 0.0005

mjs = 0.5

pbsws = 1

misws = 0.33

pbswgs = 1

+cjsws = 5e-010

cjswgs = 5e-010

pbd = 1

cid = 0.0005

mjd = 0.5

+mjswgs = 0.33

pbswd = 1

cjswd = 5e-010

mjswd = 0.33

pbswgd = 1

+cjswgd = 5e-010

mjswgd = 0.33

tpb = 0.005

tcj = 0.001

+tpbsw = 0.005

tcjsw = 0.001

tpbswg = 0.005

tcjswg = 0.001

+xtis = 3

xtid = 3

+dmcg = 0e-006

dmci = 0e-006

dmdg = 0e-006

dmcgt = 0e-007

+dwj

= 0e-008

xgw

= 0e-007 xgl = 0e-008

rshg = 0.4

gbmin = 1e-010

rbpb = 5

rbpd = 15

+rbps = 15

rbdb = 15

rbsb = 15

ngcon = 1

```

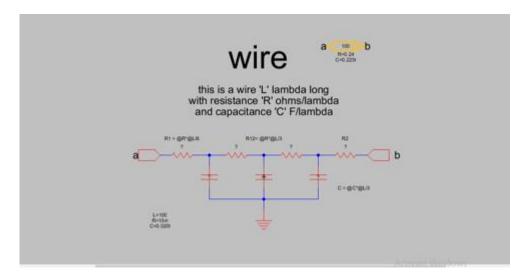

#### ELECTRIC VLSI DESIGN EDA TOOL

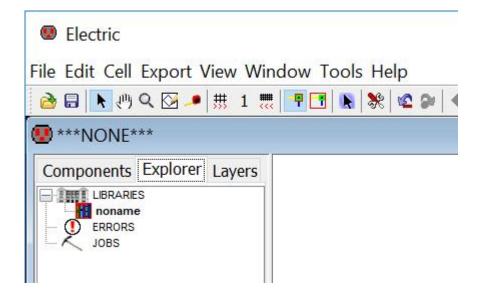

1. Start Electric: The following window will appear.

- 2. Towards the bottom of the window, Electric Messages Window will be found where different messages can be found throughout any design.

- 3. The background color of the window can change as follows

Window -> Color Schemes -> White Background Colors

4. Let's create a Library

Go to **Explorer** (beside the **Components** view); you will find **LIBRARIES** name as no name

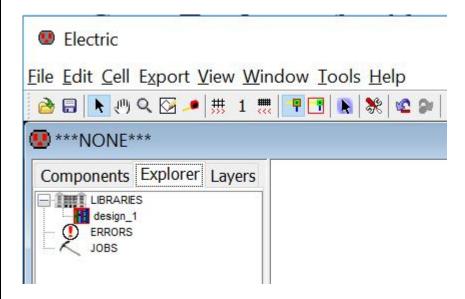

### 5. File -> Save Library As

Go to the location where design have to be save. (eg: \$PATH/Electric/Designs)

Name the design (library name) eg. design\_1.jelib

We would create our schematic and layout under this library

Now you will see design\_1.jelib under LIBRARIES name in Explorer

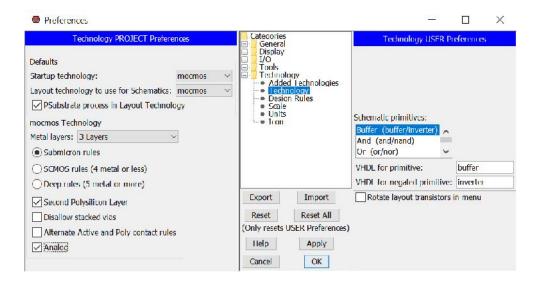

- 6. Go to Preferences by clicking the following button or executing File -> Preferences...

- 7. Then you have to set the following.

Preferences -> Categories -> Technology -> Technology

mocmos Technology -> Metal layers -> 3 Layers

Keep submicron rules and Second Polysilicon Layer checked

Click the Analog checkbox.

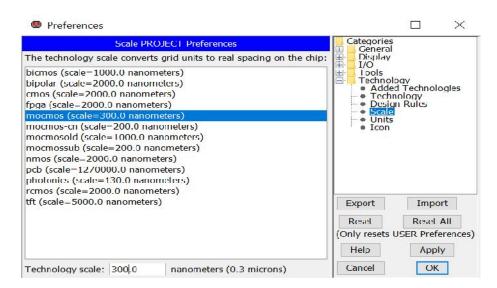

8. To set the scale go to

File -> Preferences -> Technology -> Scale and set mocmos scale to 300 nm

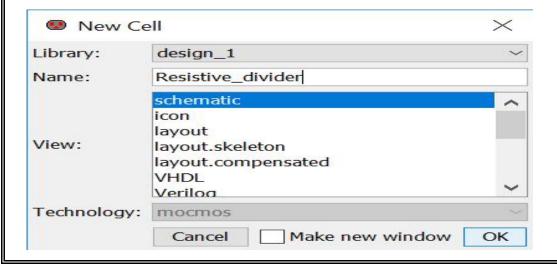

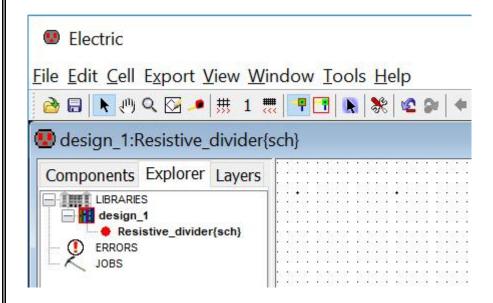

#### 9. Creating a new cell

Go to cell -> New Cell (or you can press ctrl + N). You will find a window like following.

Enter the **name** of the cell {------} and click the **view** as {schematic}.

Press ok.

Now under the **library design\_1.jelib** you can find a **schematic cell** named as **------ {sch}** with a **red indicator** as follows.

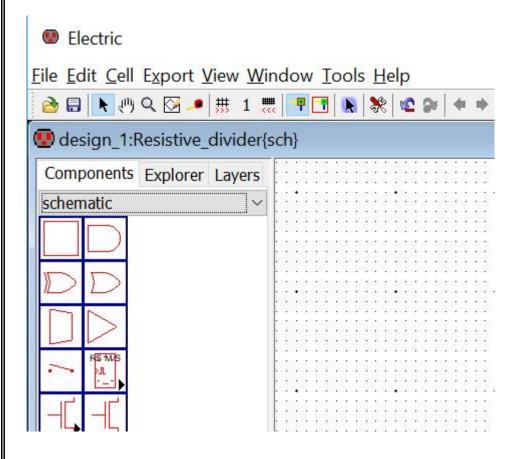

10. Now Press the **Components**. You will find the schematic components unlike the layout components in the startup window.

- 11. Now we are finished with the setup and ready to fabricate a chip in the C5 process via MOSIS

- 12. Checking of DRC (Design Rule Check)

To check DRC you can execute Tools -> DRC -> Check Hierarchically or you can press F5.

Once DRC is checked, you can see result in the **message window** as follows:

13. Layout vs. Schematic (LVS) in Electric is checked using Network Consistency Checking (NCC)

To check this, execute Tools -> NCC -> Schematic and Layout views of Cell in Current Window. You can run this command being in any design window (schematic / layout).

We found a message like sizes not checked.

For this we have to take care of the following

Go to File -> Preferences -> Categories -> Tools -> NCC -> Check transistor sizes

Once again execute the NCC, now you will find the following message.

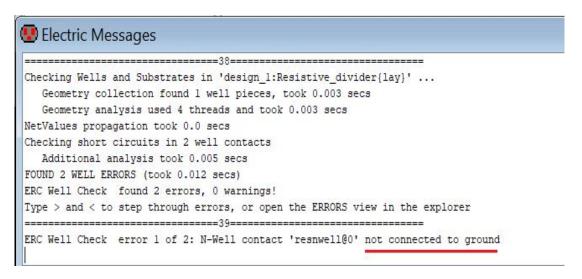

#### 14. Checking ERC (Well Check)

This process checks the connection of the n-well and p-substrate.

The C5 process used here is an n-well process. The p-type substrate is common to all NMOS devices and should be grounded.

One of the **electrical rule checks** (ERCs) is to verify that the **p-well** (in this case p-substrate) is always connected to **ground**.

Further, in this n-well process, if the design contains only **digital circuits** then the **n-well** should be connected to  $V_{DD}$ .

For Well Check execute Tools -> ERC -> Check Wells or press W (as we have bounded this key to Well Check).

The reason is as below:

In Digital Design all the N-Wells to be connected to  $V_{DD}$  and all the P-Wells to be connected to Ground.

Here we can see For N-Well, Must connect to Power is checked.

But this Resistive\_divider is not a digital design. Here the N-Well is used as a resister which is an **anlog design**.

So uncheck "Must connect to Power" under "For N-Well". You will find zero Well Check error.

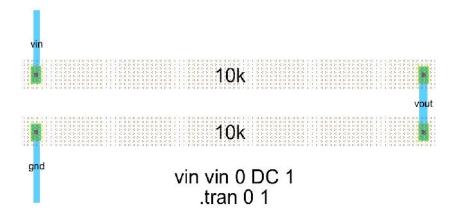

#### 15. Schematic Simulation

Now we would **simulate** the resistive divider circuit which has been built, and would observe the output voltage w.r.t. a particular input voltage.

For this we need to write a **SPICE code** which would give the description of the input voltage and would indicate the type of simulation we want to perform.

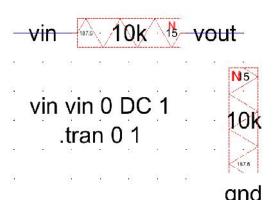

#### **Writing SPICE Code**

Go to the **Components menu**. Click on the arrowhead in the **Misc box** to add **SPICE code** to the schematic as seen in the figure.

Place the SPICE code in the **schematic** and use Ctrl+I to edit its properties.

Ensure, in the SPICE code property box, that the **Multi-line Text box is checked**.

Add the code shown in the figure for specifying a **SPICE transient analysis** and an **input voltage source**. The code indicates an input voltage of 1 V DC is applied to the circuit. The analalysis would be a transient one for 1 second.

Press F5 to check the schematic.

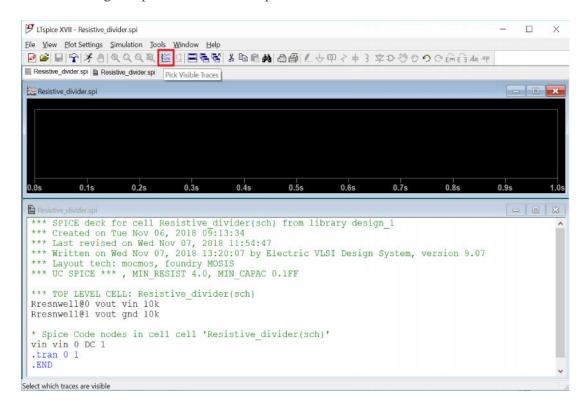

#### 16. Simulation of the Schematic

Go to Tools -> Simulation (Spice) -> Write Spice Deck.

The following LTspice window will open.

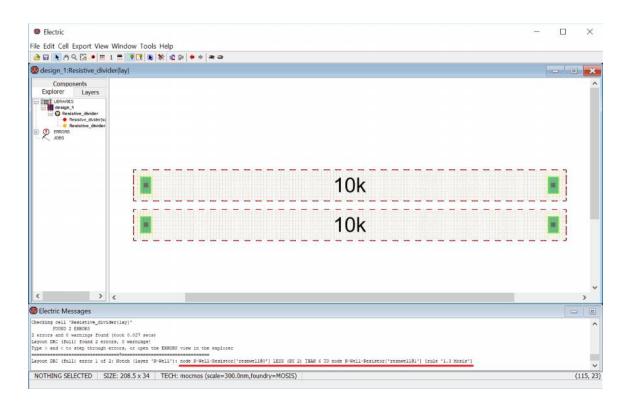

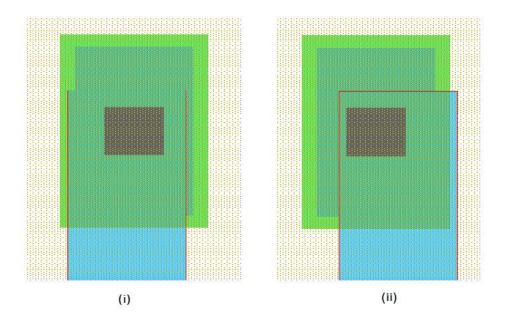

#### 17. Resistive Divider Layout

Open the layout view of the Resistive\_divider cell and then copy/paste (Ctrl+C/Ctrl+V) an **additional resistor**.

Running a **DRC** (pressing F5) on the above layout results in the following **error**.

By pressing > we see that there is **too little space between the N-wells**.

**Move the Nodes apart** until the layout passes the DRCs. Of-course the error will not appear if you have initially placed both the resistors apart enough, which would **satisfy the MOSIS rule** for space between N-wells.

Run DRC to check the design is free of error or not.

This layout cell should match the schematic cell. Verify this by running the NCC (aka LVS check).

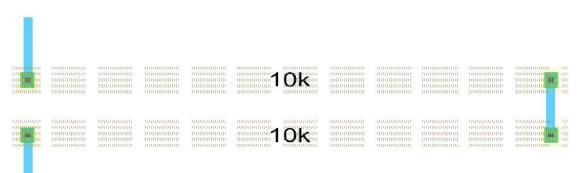

The following figure shows the Electric Messages for **DRC** of layout and **NCC** of both layout and schematic (LVS).

## **18. Layout Simulation**

The following figure shows the visible spice code.

Run a DRC, NCC, and a Well Check to ensure that there aren't any errors.

This cell can be simulated following the same steps used for simulating the schematic view above.

Simulate this cell using LTspice now.

The following figure shows the simulation output from LTspice for the Resistive\_divider layout.

```

* BSIM3 models for AMI Semiconductor's C5 process

* Don't forget the .options scale=300nm if using drawn lengths

* and the MOSIS SUBM design rules

* 2<Ldrawn<500 10<Wdrawn<10000 Vdd=5V

* Note minimum L is 0.6 um while minimum W is 3 um

* Change to level=49 when using HSPICE or SmartSpice

.MODEL NMOS NMOS (

LEVEL = 8

+VERSION = 3.1

TNOM = 27

TOX = 1.39E-8

+XJ

= 1.5E-7

NCH

= 1.7E17

VTH0 = 0.6696061

K2

= -0.0839158 K3

+K1

= 0.8351612

= 23.1023856

= -7.6841108 W0 = 1E-8

NLX = 1E-9

+K3B

+DVT0W = 0

DVT1W = 0

DVT2W = 0

+DVT0 = 2.9047241

DVT1 = 0.4302695

DVT2 = -0.134857

+U0

= 458.439679

UA

= 1E-13

UB

= 1.485499E-18

+UC

= 1.629939E-11 VSAT = 1.643993E5

A0

= 0.6103537

+AGS = 0.1194608

B0

= 2.674756E-6 B1

= 5E-6

+KETA = -2.640681E-3 A1

= 8.219585E-5 A2

= 0.3564792

+RDSW = 1.387108E3

PRWG = 0.0299916 PRWB = 0.0363981

WINT = 2.472348E-7 LINT = 3.597605E-8

+WR

= 1

+XL

=0

XW

=0

DWG = -1.287163E-8

+DWB = 5.306586E-8 \text{ VOFF} = 0

NFACTOR = 0.8365585

+CIT

=0

CDSC = 2.4E-4

CDSCD = 0

+CDSCB = 0

ETA0 = 0.0246738

ETAB = -1.406123E-3

+DSUB = 0.2543458

PCLM = 2.5945188

PDIBLC1 = -0.4282336

+PDIBLC2 = 2.311743E-3 PDIBLCB = -0.0272914

DROUT = 0.7283566

+PSCBE1 = 5.598623E8

PSCBE2 = 5.461645E-5 PVAG = 0

+DELTA = 0.01

RSH = 81.8

MOBMOD = 1

UTE = -1

KT1

+PRT

= 8.621

= -0.2501

+KT1L = -2.58E-9

KT2

=0

UA1

= 5.4E-10

```

```

+UB1 = -4.8E-19   UC1 = -7.5E-11   AT = 1E5

+WL = 0 WLN = 1 WW = 0

WWL = 0 \qquad LL = 0

+WWN = 1

+LLN = 1

LW = 0 \qquad LWN = 1

CAPMOD = 2 XPART = 0.5

+LWL = 0

+CGDO = 2E-10 CGSO = 2E-10 CGBO = 1E-9

+CJ = 4.197772E-4 PB = 0.99 MJ = 0.4515044

+CJSW = 3.242724E-10 PBSW = 0.1 MJSW = 0.1153991

+CJSWG = 1.64E-10 	 PBSWG = 0.1

MJSWG = 0.1153991

+CF = 0 PVTH0 = 0.0585501 PRDSW = 133.285505

+PK2 = -0.0299638 WKETA = -0.0248758 LKETA = 1.173187E-3

+AF = 1 KF = 0)

.MODEL PMOS PMOS (

LEVEL = 8

+VERSION = 3.1 TNOM = 27 TOX = 1.39E-8

+XJ = 1.5E-7 NCH = 1.7E17 VTH0 = -0.9214347

K1 = 0.5553722 K2 = 8.763328E-3 K3 = 6.3063558

+K3B = -0.6487362 \quad W0 = 1.280703E-8 \quad NLX = 2.593997E-8

+DVT0W = 0 DVT1W = 0 DVT2W = 0

+DVT0 = 2.5131165 DVT1 = 0.5480536 DVT2 = -0.1186489

+U0 = 212.0166131 \text{ UA} = 2.807115\text{E-9} \text{ UB} = 1\text{E-21}

+UC = -5.82128E-11 VSAT = 1.713601E5 A0 = 0.8430019

+AGS = 0.1328608 \quad B0 = 7.117912E-7 \quad B1 = 5E-6

KETA = -3.674859E-3 A1 = 4.77502E-5 A2 = 0.3

+RDSW = 2.837206E3 PRWG = -0.0363908 PRWB = -1.016722E-5

+WR = 1 WINT = 2.838038E-7 LINT = 5.528807E-8

+XL = 0 XW = 0 DWG = -1.606385E-8

+DWB = 2.266386E-8 VOFF = -0.0558512 NFACTOR = 0.9342488

+CIT = 0 CDSC = 2.4E-4 CDSCD = 0

+CDSCB = 0 ETA0 = 0.3251882 ETAB = -0.0580325

DSUB = 1 PCLM = 2.2409567 PDIBLC1 = 0.0411445

+PDIBLC2 = 3.355575E-3 PDIBLCB = -0.0551797 DROUT = 0.2036901

```

```

+DELTA = 0.01 RSH = 101.6 MOBMOD = 1

+PRT = 59.494 UTE = -1 KT1 = -0.2942

+KT1L = 1.68E-9 KT2 = 0 UA1 = 4.5E-9

+UB1 = -6.3E-18 UC1 = -1E-10 AT = 1E3

+WL = 0 WLN = 1 WW = 0

+WWN = 1

WWL = 0

LL = 0

+LLN = 1 LW = 0 LWN = 1

+LWL = 0 CAPMOD = 2 XPART = 0.5

+CGDO = 2.9E-10 	 CGSO = 2.9E-10 	 CGBO = 1E-9

+CJ = 7.235528E-4 PB = 0.9527355 MJ = 0.4955293

+CJSW = 2.692786E-10 PBSW = 0.99

MJSW = 0.2958392

+CJSWG = 6.4E-11 PBSWG = 0.99 MJSWG = 0.2958392

+CF = 0 PVTH0 = 5.98016E-3 PRDSW = 14.8598424

+PK2 = 3.73981E-3 WKETA = 5.292165E-3 LKETA = -4.205905E-3

```

AF = 1 KF = 0

| EXP NO: 7 | Ring Oscillator |

|-----------|-----------------|

| Date:     |                 |

To design, analyze and simulate the ring oscillator using LT-SPICE.

## **APPARATUS REQUIRED:**

| S.No | Nameofthe equipment/ software | Quantity |

|------|-------------------------------|----------|

| 1.   | PC with Windows               | 1        |

| 2.   | LT-SPLICE                     | 1        |

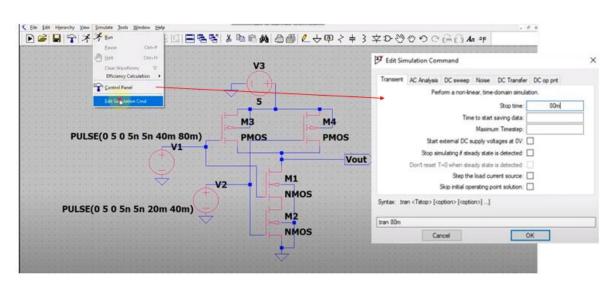

#### **PROCEDURE:**

- 1. Start "LTSpice XVII" (or earlier version)

- 2. Start a new Project under the File -> New Schematic

- 3. Make sure, files are saved in a convenient directory. The root directory (C:\) or Desktop are probably not good choices. I would suggest creating a directory "C:\Circuits" and saving your work there

- 4. Double click on LTspice XVII item  $\rightarrow$  Select the file menu  $\rightarrow$  double click save button

- 5. Click on component button → click type nmos → click on nmos4 item → select ok → click left in screen → press cntl+E for required number of nmos

- 6. Follow step 5 for selecting pmos4 device.

- 7. Click on wire button and give connection in circuit diagram

- 8. Click the ground button and place in screen and give connection using wire.

- 9. Click voltage in component list and place in screen. Give connection using wire.

- 10. Click on spice directive button and type ".include level 3 and 54.txt" then click ok

- 11. Click File menu → select save as and select desktop item outline item and select the file name and type the name of file then give ok.

- 12. Click on run button.

- 13. Obtain the Transient analysis of Ring oscillator

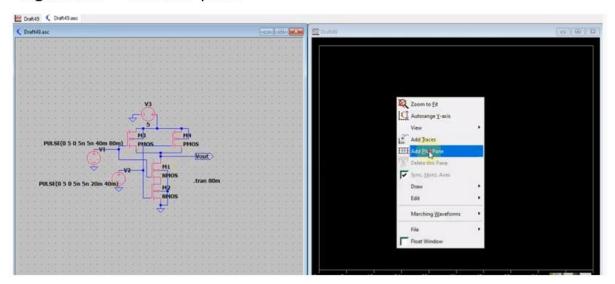

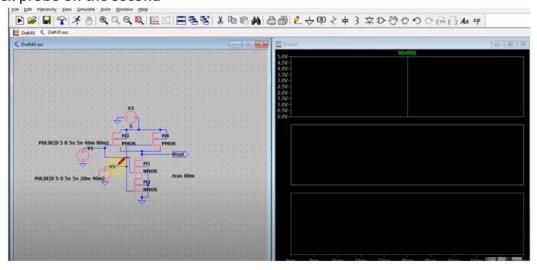

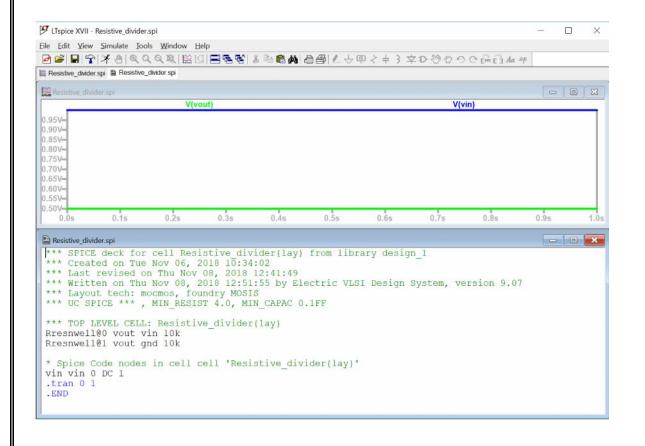

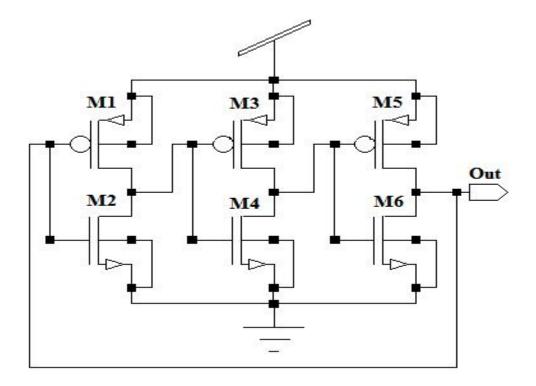

# **Circuit Diagram:**

3 stage ring oscillator

3 stage ring oscillator using CMOS

## **SCHEMATIC:**

| Calcu | lation: |

|-------|---------|

| Cuicu | iauoii. |

The frequency of oscillation formula for ring oscillator is

$$f = \frac{1}{2n}$$

Here T = time delay for single inverter

n = number of inverters in the oscillator

## **RESULT:**

Thus the Ring oscillator is simulated using LT-SPICE.

| EVD NO. 0        |                        |

|------------------|------------------------|

| <b>EXP NO: 8</b> | Differential Amplifier |

| Date:            | <b>F</b>               |

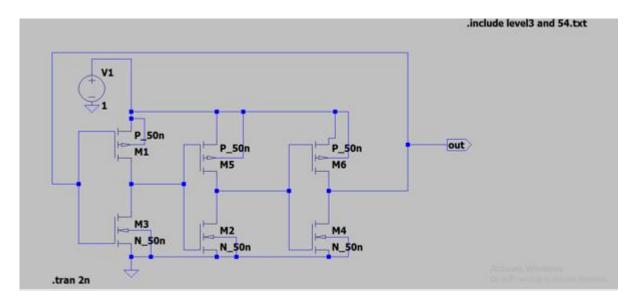

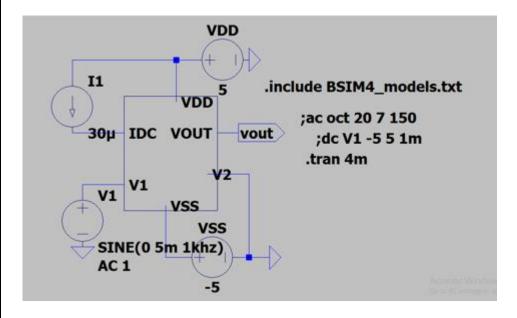

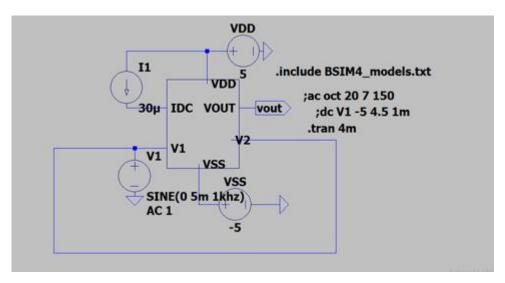

To design, analyze and simulate the Differential Amplifier using LT-SPICE.

## **APPARATUS REQUIRED:**

| S.No | Nameofthe equipment/ software | Quantity |

|------|-------------------------------|----------|

| 1.   | PC with Windows               | 1        |

| 2.   | LT-SPLICE                     | 1        |

#### **PROCEDURE:**

- 1. Start "LTSpice XVII" (or earlier version)

- 2. Start a new Project under the File -> New Schematic

- 3. Make sure, files are saved in a convenient directory. The root directory (C:\) or Desktop are probably not good choices. I would suggest creating a directory "C:\Circuits" and saving your work there

- 4. Double click on LTspice XVII item → Select the file menu → double click save button

- 5. Click on component button → click type nmos → click on nmos4 item → select ok → click left in screen → press cntl+E for required number of nmos

- 6. Follow step 5 for selecting pmos4 device.

- 7. Connect the Circuit as schematic.

- 8. Click on spice directive button and type ".include BISM4\_models.txt" then click ok

- 9. Click File menu → select save as and select desktop item outline item and select the file name and type the name of file then give ok.

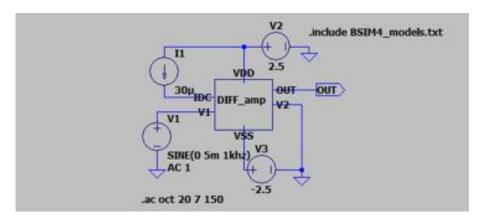

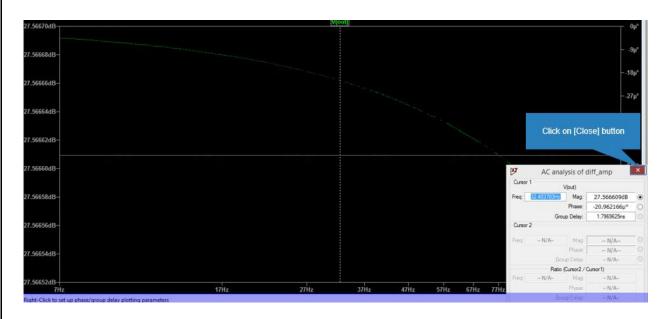

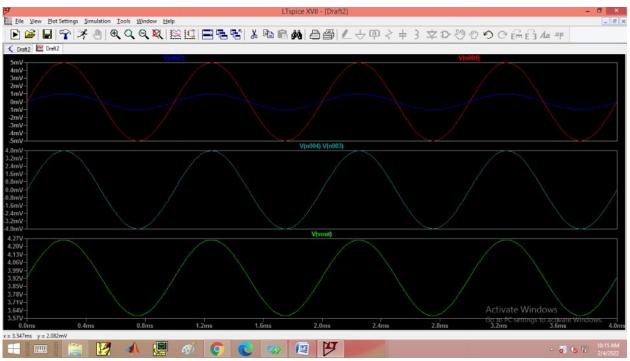

- 10. .To Obtain the AC analysis, Click on spice directive button and type ".ac oct 20 7 150" then click ok

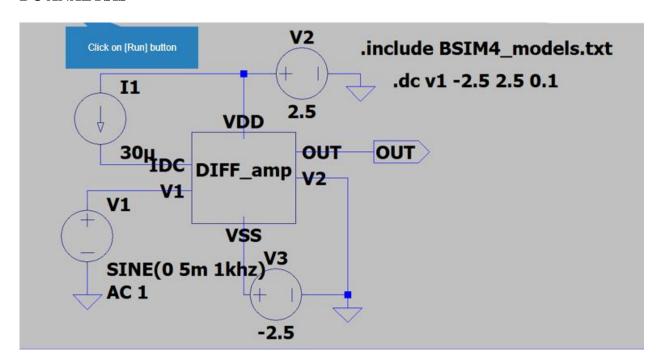

- 11. To Obtain the DC analysis, Click on spice directive button and type ".dc V1 -5 5 1m" then click ok

- 12. To Obtain the Transient analysis, Click on spice directive button and type ".tran 4m" then click ok

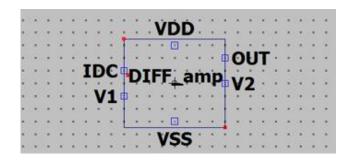

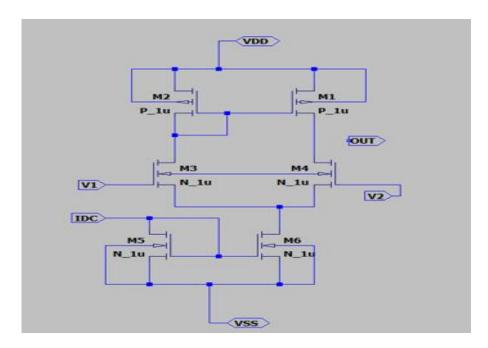

# **SCHEMATIC:**

# **Symbol:**

## **Circuit:**

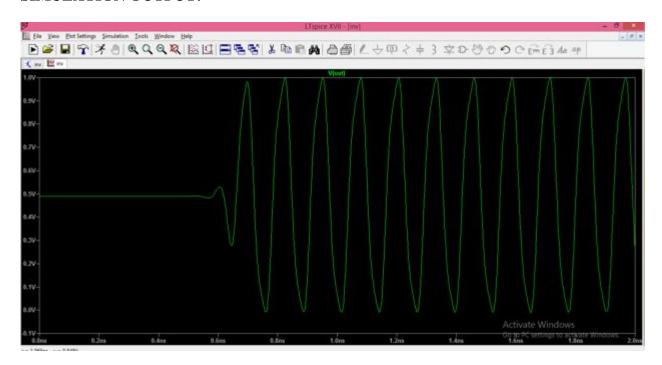

## **AC ANALYSIS:**

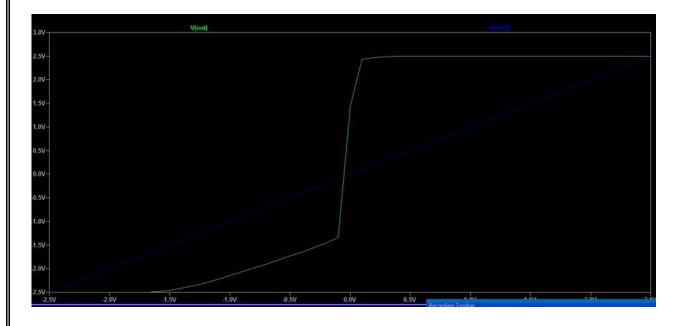

## DC ANALYSIS

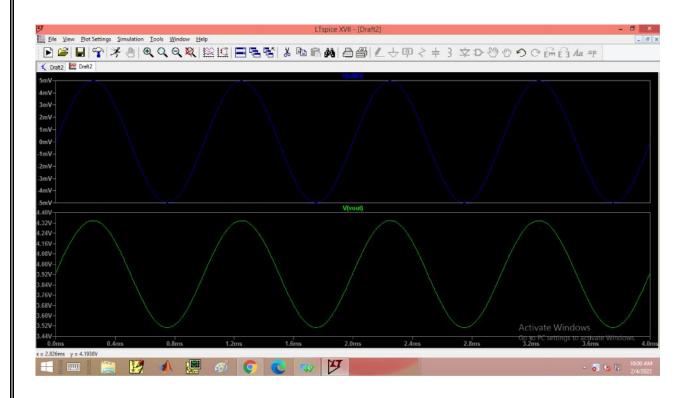

# **Transient Analysis:**

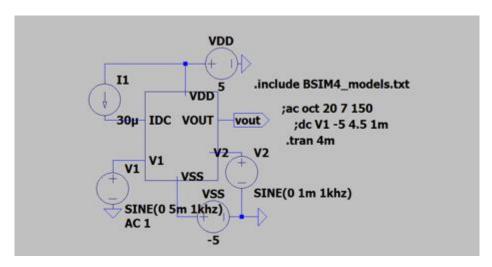

## Differential Mode Gain:

## Common Mode Gain:

Calculation:

$$C = \frac{A_D}{A_C}$$

$$C \quad \text{if } d = 20 \text{ le } \frac{A_D}{A_C}$$

$$A_D = D \quad V \quad G$$

$$A_D = \frac{V_O}{V1 - V2}$$

V1= 5mv V2= 1mv Vout =

$$A_C = C\epsilon$$

$m$   $V$   $G$

$$A_C = \frac{V_o}{(V1 + V2)/2}$$

V1=5mv V2=5mv Vout =

## **RESULT:**

Thus the Differential Amplifier is simulated and CMRR is determined using LT-SPICE.

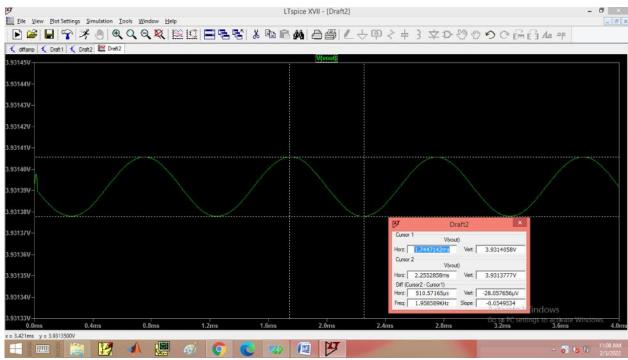

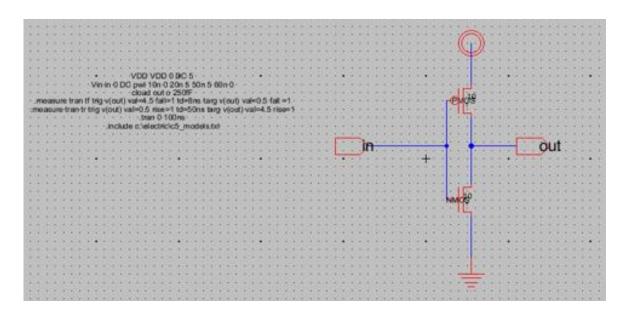

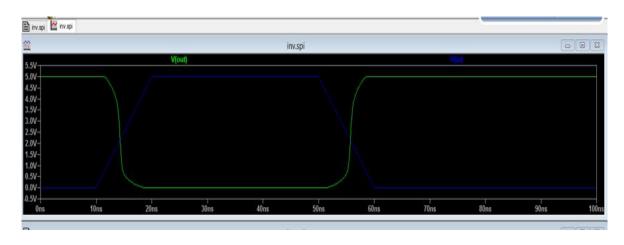

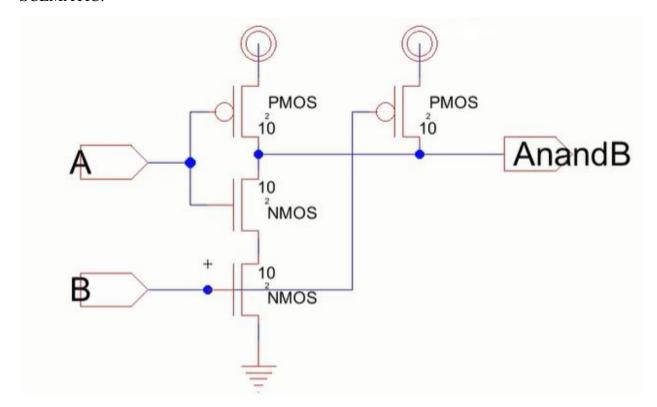

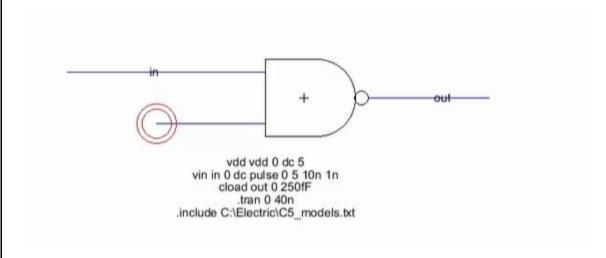

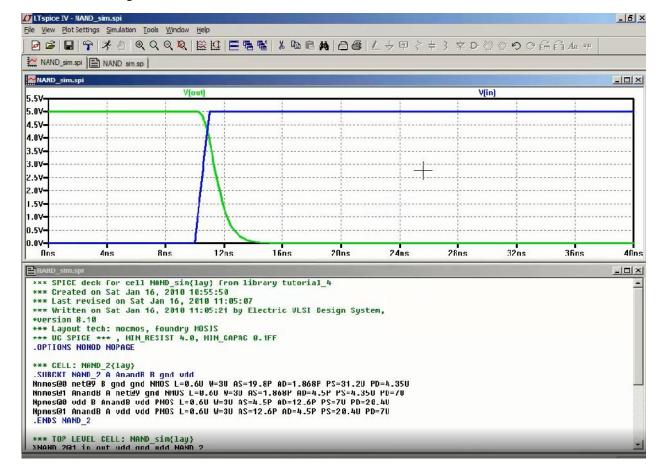

| EXP NO: 9<br>Date: | CMOS Inverter |

|--------------------|---------------|

| Date.              |               |

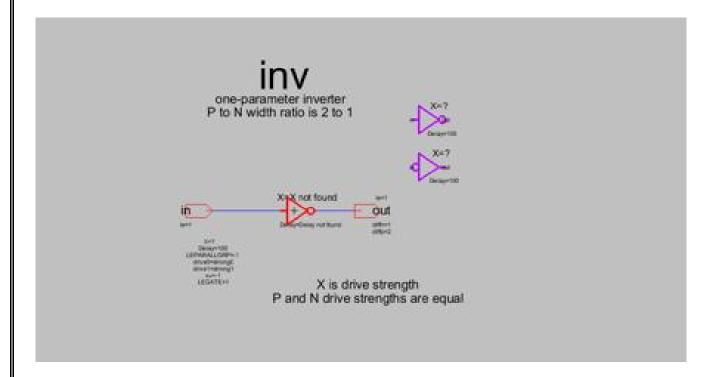

To design a CMOS inverter using the Schematic entry tool - Electric and verify its functioning. **APPARATUS REQUIRED:**

| S.No | Nameofthe equipment/ software | Quantity |

|------|-------------------------------|----------|

| 1.   | PC with Windows               | 1        |

| 2.   | ELECTRIC-EDA Tool             | 1        |

#### **PROCEDURE:**

- 1. Start Electric VLSI system Design tool.

- 2. Start a new Project under the File -> New Schematic

- 3. Make sure, files are saved in a convenient directory. Save as filename.jelib under LIBRARIES name in Explorer

- 4. Go to Preferences by clicking the following button or executing File -> Preferences Then set the following.

- a. Preferences -> Categories -> Technology -> Technology

- 5. Go to cell → New Cell → Schematic

- 6. Go to **Components**. The schematic components will appear unlike the layout components in the startup window.

- 7. Connect the Circuit as shown in Figure

- 8. To check DRC , execute Tools -> DRC -> Check Hierarchically

- 9. To check NCC, execute Tools -> NCC -> Schematic and Layout views of Cell in Current Window.

- 10. **For Well Check** execute Tools -> ERC -> Check Wells

- 11. Go to the **Components menu**. Click on the arrowhead in the **Misc box** to add **SPICE code** to the schematic . Place the SPICE code in the **schematic**

- 12. Go to Tools -> Simulation (Spice) -> Write Spice Deck.

- 13. Obtain the output waveform of CMOS Inverter.

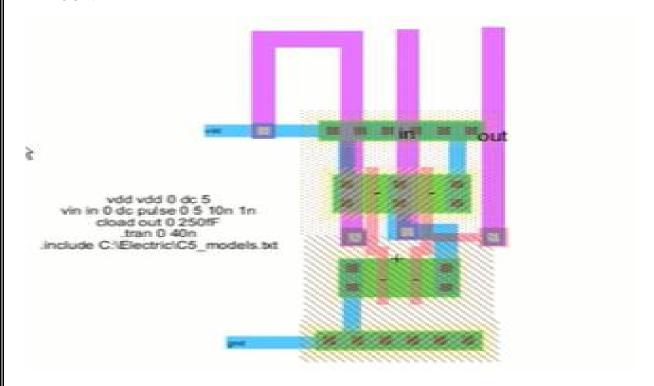

## **SCHEMATIC**

## Symbol:

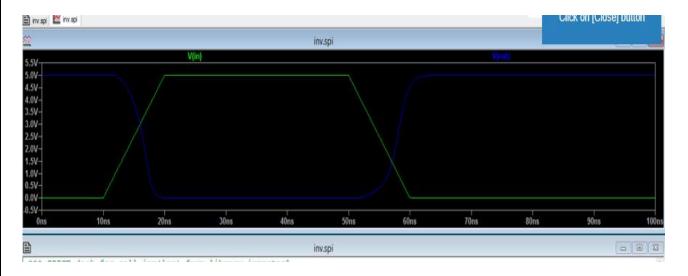

## SIMULATION OUTPUT:

# RESULT

Thus the design & simulation of a CMOS inverter has been carried out using schematic of Electric EDA Tools.

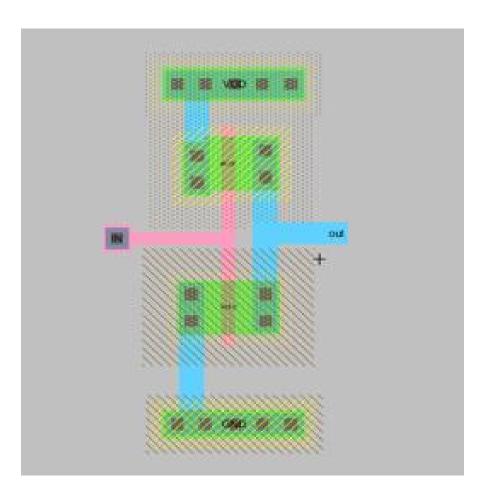

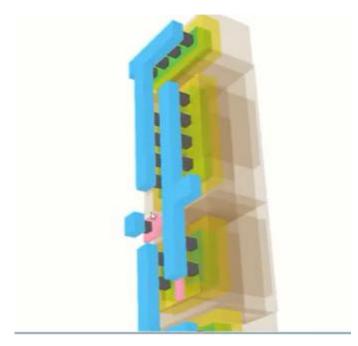

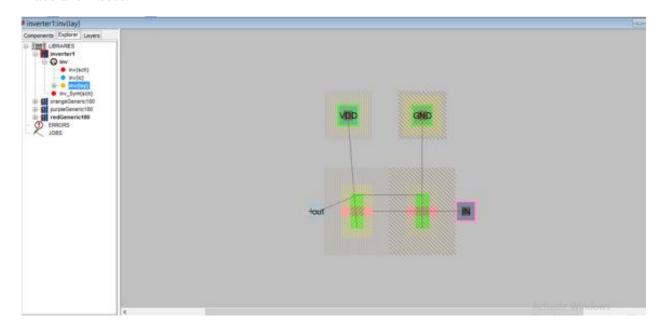

| EXP NO: 10 Date: Layout CMOS Inverter |

|---------------------------------------|

|---------------------------------------|

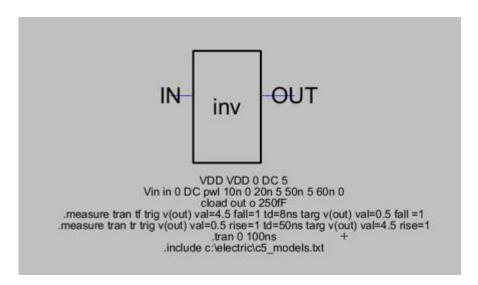

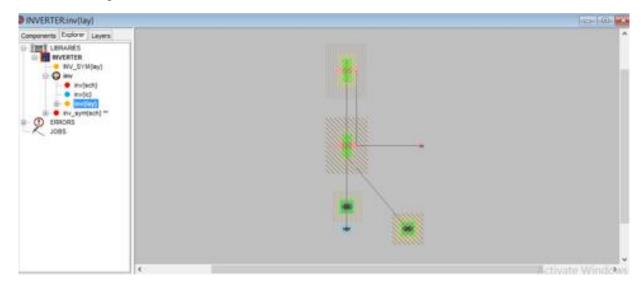

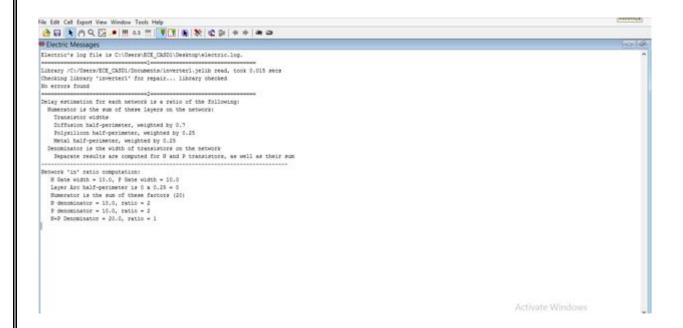

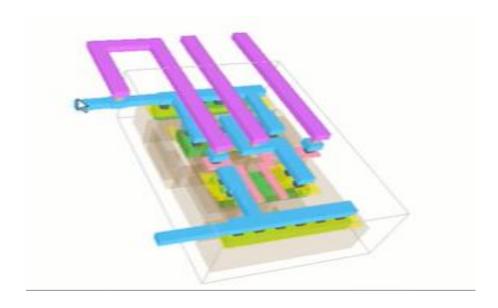

To draw the layout of CMOS Inverter using Electric EDA tool and extract the SPICE code.

#### **APPARATUS REQUIRED:**

| S.No | Nameofthe equipment/ software | Quantity |

|------|-------------------------------|----------|

| 1.   | PC with Windows               | 1        |

| 2.   | ELECTRIC-EDA Tool             | 1        |

#### **PROCEDURE:**

- 1. Start Electric VLSI system Design tool.

- 2. Start a new Project under the File -> New Schematic

- 3. Make sure, files are saved in a convenient directory. Save as filename.jelib under LIBRARIES name in Explorer

- 4. Go to Preferences by clicking the following button or executing File -> Preferences Then set the following.

- a. Preferences -> Categories -> Technology -> Technology

- 5. Go to cell → New Cell → Schematic

- 6. Go to **Layers**. The Layer components will appear unlike the schematic components in the components window.

- 7. Connect the Layout as shown in Figure

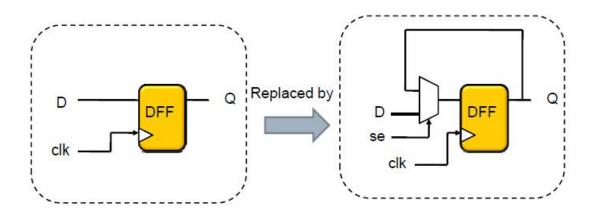

- 8. To check DRC ,execute Tools -> DRC -> Check Hierarchically